## Efficient Polynomial Evaluation Algorithm and Implementation on FPGA

by

### Simin Xu

School of Computer Engineering

A thesis submitted to Nanyang Technological University in partial fullfillment of the requirements for the degree of Master of Engineering

### Abstract

In this thesis, an optimized polynomial evaluation algorithm is presented. Compared to Horner's Rule which has the least number of computation steps but longest latency, or parallel evaluation methods like Estrin's method which are fast but with large hardware overhead, the proposed algorithm could achieve high level of parallelism with smallest area, by means of replacing multiplication with square.

To enable the performance gain for the proposed algorithm, an efficient integer squarer is proposed and implemented in FPGA with fewer DSP blocks. Previous work has presented tiling method for a double precision squarer which uses the least amount of DSP blocks so far. However it incurs a large LUT overhead and has a complex and irregular structure that it is not expandable for higher word size. The circuit proposed in this thesis can reduce the DSP block usage by an equivalent amount compared to the tiling method while incurring a much lower LUT overhead: 21.8% fewer LUTs for a 53-bit squarer. The circuit is mapped to Xilinx Virtex 6 FPGA and evaluated for a wide range of operand word sizes, demonstrating its scalability and efficiency.

With the novel squarer, the proposed polynomial algorithm exhibits 41% latency reduction over conventional Horner's Rule for a  $5^{th}$  degree polynomial with 11.9% less area and 44.8% latency reduction in a  $4^{th}$  degree polynomial with 5% less area on FPGA. In contrast, Estrin's method occupies 26% and 16.5% more area compared to Horner's Rule to achieve same level of speed improvement for the same  $5^{th}$  and  $4^{th}$  degree polynomial respectively.

## Acknowledgments

First of all, I feel tremendously lucky to have Professor Ian McLoughlin and Professor Suhaib Fahmy to be my supervisor. Professor Ian led me towards the field of fixed-point arithmetic and inspired me to further research on polynomial evaluation. Professor Suhaib greatly broadened my horizon in the area of reconfigurable hardware. I'd like to thank both of them for their kindness, patience, assistance and great advice.

My appreciation also goes to Eu Gene Goh, Mike Leary, Wilson Low, Susan John and Xilinx Asia Pacific (Singapore) for supporting me. Specially thank Wei Ting Loke for valuable technical discussions and comments on my research.

Last but not least, this thesis can't be finished without my family. Thanks my parents for always encouraging me and my wife for her endless love.

## **Author's Publications**

S. Xu, S. A. Fahmy, and I. V. McLoughlin, "Efficient Large Integer Squarers on FPGA" to appear in Proceedings of the IEEE Symposium on Field programmable Custom Computing Machines (FCCM), Seattle, WA, May 2013.

## Contents

|          | Abs  | stract   |                                                                | j    |

|----------|------|----------|----------------------------------------------------------------|------|

|          | Ack  | knowle   | dgments                                                        | ii   |

|          | Au   | thor's   | Publications                                                   | iii  |

|          | List | t of Fig | gures                                                          | vii  |

|          | List | t of Ta  | bles                                                           | viii |

|          | List | t of Co  | ode                                                            | Х    |

| 1        | Intr | oducti   | ion                                                            | 1    |

|          | 1.1  | Motiva   | ation                                                          | 1    |

|          | 1.2  | Scope    | Definition                                                     | 5    |

|          | 1.3  | Contri   | ibutions                                                       | 6    |

|          |      | 1.3.1    | Novel Polynomial Evaluation Algorithm                          | 6    |

|          |      | 1.3.2    | Comparison of Fixed Point Polynomial Evaluation Algorithms Im- |      |

|          |      |          | plementation on FPGA                                           | 6    |

|          |      | 1.3.3    | Novel Integer Squarer Design on FPGA                           | 6    |

|          | 1.4  | Organ    | ization of the Thesis                                          | 7    |

| <b>2</b> | Cor  | ventio   | onal Polynomial Evaluation Algorithms, Implementation and      |      |

|          | Opt  | imizat   | ion                                                            | 8    |

|          | 2.1  | Polyno   | omial Evaluation Algorithms                                    | 8    |

|          |      | 211      | Direct Method                                                  | 8    |

|   |     | 2.1.2   | Horner's Rule                                               | 9  |

|---|-----|---------|-------------------------------------------------------------|----|

|   |     | 2.1.3   | Parallel Methods                                            | 9  |

|   | 2.2 | Polyno  | omial Evaluation Implementation                             | 11 |

|   |     | 2.2.1   | Horner's Rule                                               | 13 |

|   |     | 2.2.2   | Dorn's Method                                               | 14 |

|   |     | 2.2.3   | Estrin's Method                                             | 15 |

|   | 2.3 | Polyn   | omial Evaluation Optimization                               | 16 |

| 3 | Cor | nventio | onal Arithmetic Implementation on FPGA                      | 19 |

|   | 3.1 | FPGA    | Background                                                  | 19 |

|   | 3.2 | Parall  | el Multiplier in FPGA                                       | 22 |

|   |     | 3.2.1   | Multiplier Based on LUT                                     | 22 |

|   |     | 3.2.2   | Multiplier Based on Cascaded Chains of DSP Blocks           | 22 |

|   |     | 3.2.3   | Multiplier with Fewer DSP Blocks                            | 24 |

| 4 | Cor | nventio | onal Squarer Design                                         | 26 |

|   | 4.1 | Square  | er Designed for ASICs                                       | 26 |

|   | 4.2 | Squar   | er Based on Cascaded Method                                 | 27 |

|   | 4.3 | Squar   | er Based on Non-standard Tiling Method                      | 29 |

| 5 | Nov | vel Pol | ynomial Evaluation Algorithm                                | 31 |

|   | 5.1 | First 1 | Hypothesis                                                  | 31 |

|   | 5.2 | Novel   | Method Example                                              | 32 |

|   | 5.3 | Gener   | alized Format                                               | 34 |

|   | 5.4 | Deriva  | ation of the Coefficient Set and Accuracy Concern           | 36 |

|   | 5.5 | Motiv   | ation of Squarer and Reconfigurable Hardware Implementation | 38 |

| 6            | Nov   | vel Squarer Implementation on FPGA                  | 39        |

|--------------|-------|-----------------------------------------------------|-----------|

|              | 6.1   | Proposed Design                                     | 39        |

|              |       | 6.1.1 Squarers for Three Splits Input               | 39        |

|              |       | 6.1.2 Squarer for Four Splits and More              | 43        |

|              | 6.2   | Implementation Results                              | 48        |

| 7            | Imp   | olementation of Polynomial Evaluator on FPGA        | <b>52</b> |

|              | 7.1   | Function Evaluator in FloPoCo                       | 53        |

|              | 7.2   | Polynomial Evaluator using Estrin's Method          | 56        |

|              | 7.3   | Polynomial Evaluator using Proposed Method          | 60        |

|              | 7.4   | Implementation Results                              | 66        |

| 8            | Cor   | nclusion                                            | 69        |

| $\mathbf{R}$ | efere | nces                                                | 71        |

| $\mathbf{A}$ | ppen  | dix A Supplementary Figures Tables and Source codes | 77        |

## List of Figures

| 2.1 | Diagram for evaluating $5^{th}$ degree polynomials using Horner's Rule      | 13 |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | Diagram for evaluating $5^{th}$ degree polynomials using Dorn's method      | 14 |

| 2.3 | Diagram for evaluating $5^{th}$ degree polynomials using Estrin's method    | 16 |

| 2.4 | Function with range reduction                                               | 17 |

| 2.5 | Function with sub-intervals                                                 | 17 |

| 3.1 | Simplified diagram of LUT, multipliexer, flip flops and carry chains in CLB |    |

|     | in Xilinx Virtex 6 FPGA                                                     | 20 |

| 3.2 | Simplified diagram of DSP48E1 in Xilinx Virtex 6 FPGA                       | 21 |

| 3.3 | Partial product alignment of $4\times4$ bit parallel multiplier             | 22 |

| 3.4 | Pipeline schematic of general purpose multiplier                            | 23 |

| 3.5 | Tiling multiplier example                                                   | 25 |

| 4.1 | Partial product alignment of $4 \times 4$ parallel squarer                  | 27 |

| 4.2 | Pipeline schematic of squarer based on cascading DSP chains                 | 28 |

| 4.3 | Tiling method for square                                                    | 30 |

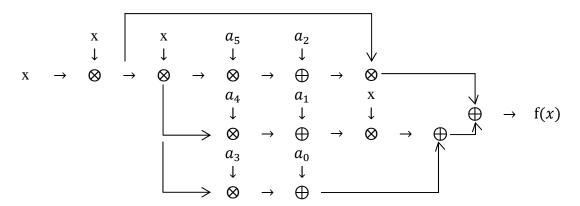

| 5.1 | Diagram for evaluating $5^{th}$ degree polynomials using proposed method    | 33 |

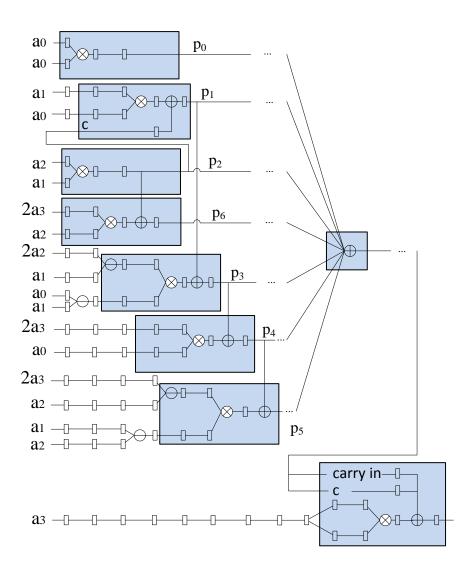

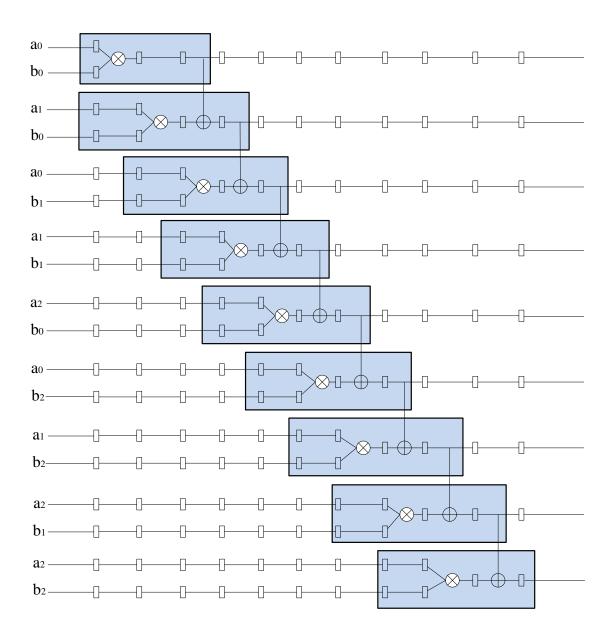

| 6.1 | Pipeline schematic of squarer for three splits input                        | 42 |

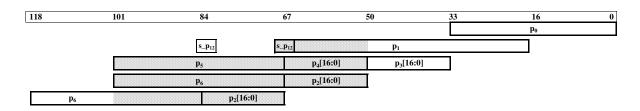

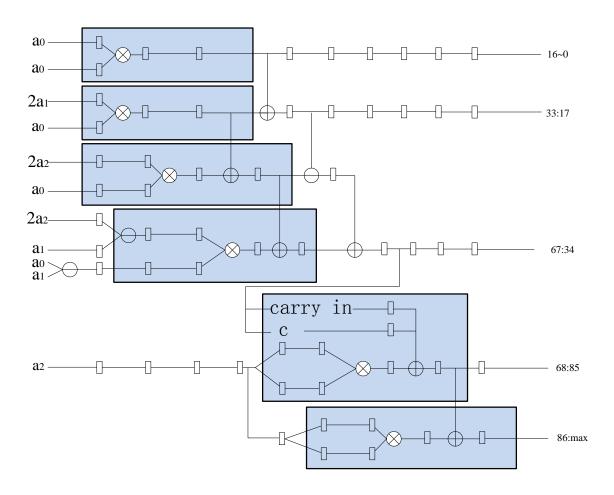

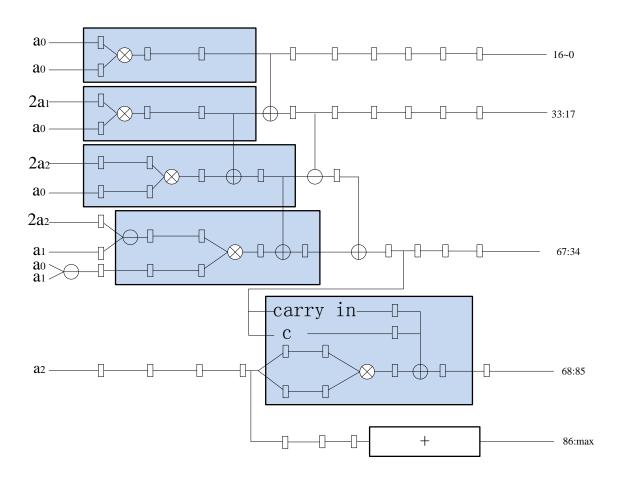

| 6.2 | Adder alignment of squarer for four splits input                            | 45 |

| 6.3 | Pipeline schematic of squarer for four splits input                         | 46 |

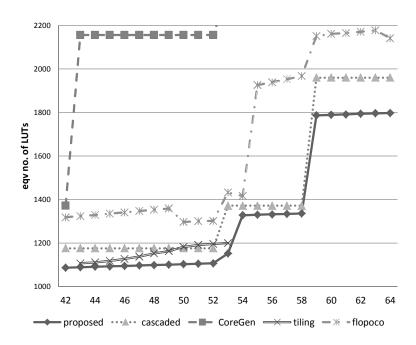

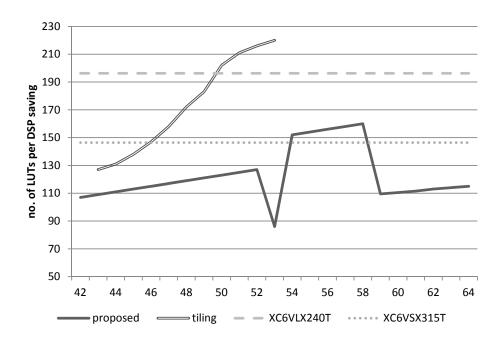

| 6.4 | Equivalent LUT usage for all methods against operand word length        | 49 |

|-----|-------------------------------------------------------------------------|----|

| 6.5 | LUTs per DSP saved (from the cascaded method) ratio for tiling and      |    |

|     | proposed methods against operand word length                            | 50 |

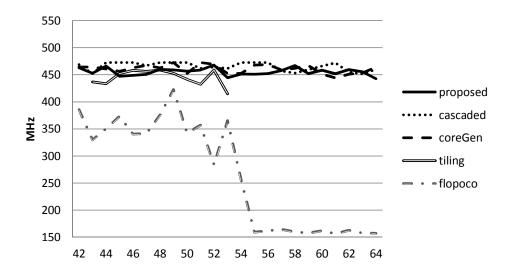

| 6.6 | Maximum frequency for all methods against operand word length           | 51 |

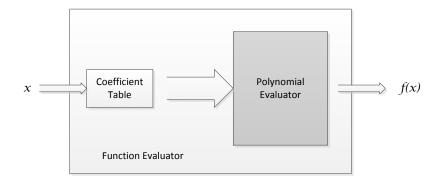

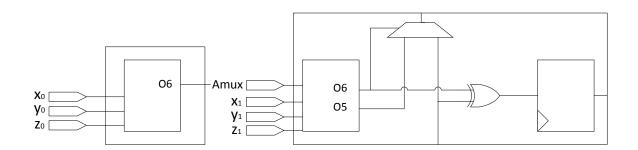

| 7.1 | System diagram of fixed point function evaluator                        | 52 |

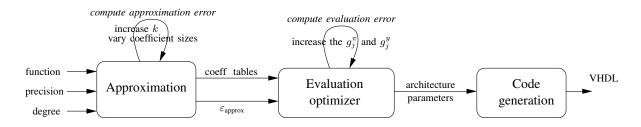

| 7.2 | Procedure of generating function evaluator                              | 54 |

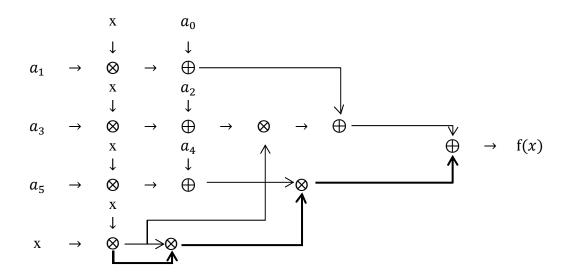

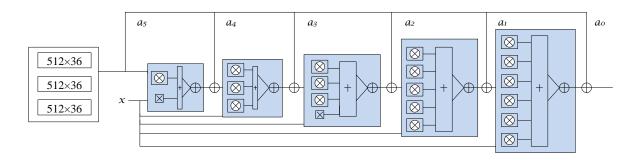

| 7.3 | Schematic of $5^{th}$ degree polynomial evaluator                       | 56 |

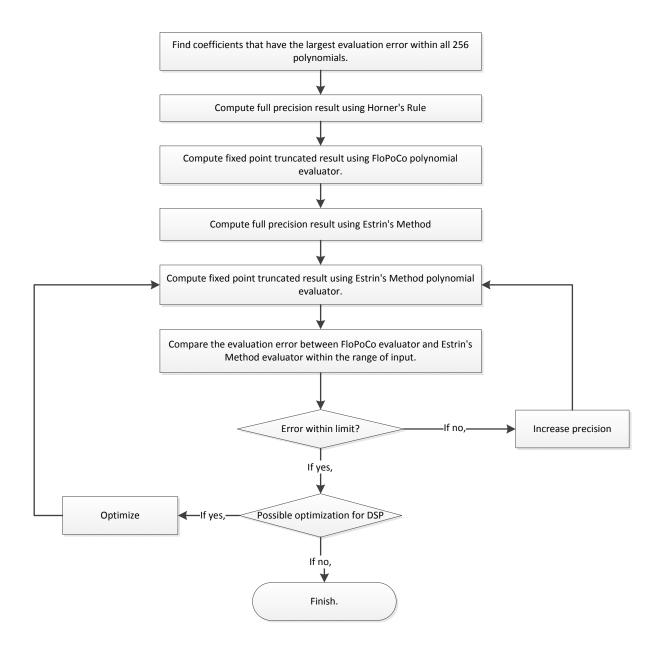

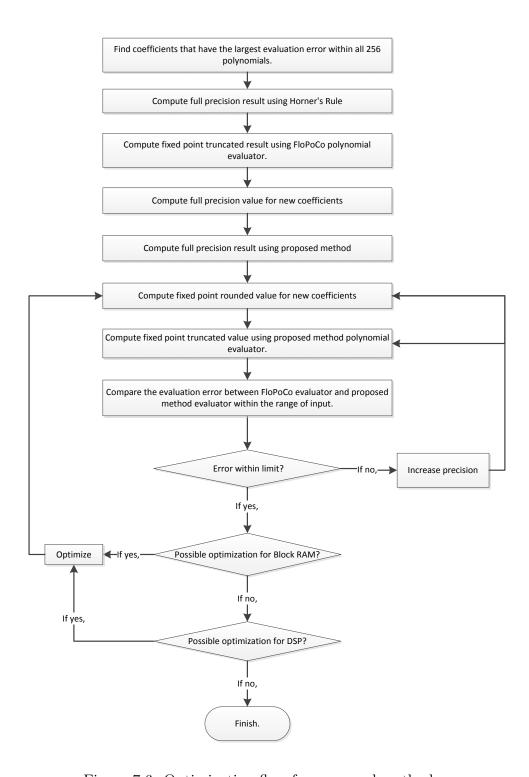

| 7.4 | Optimization flow for Estrin's method                                   | 58 |

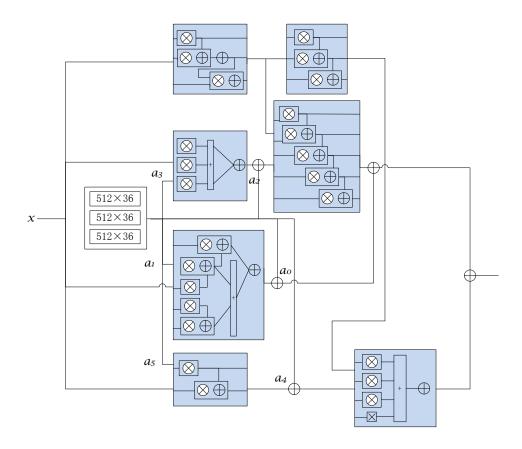

| 7.5 | Schematic of $5^{th}$ degree polynomial evaluator using Estrin's method | 61 |

| 7.6 | Optimization flow for proposed method                                   | 63 |

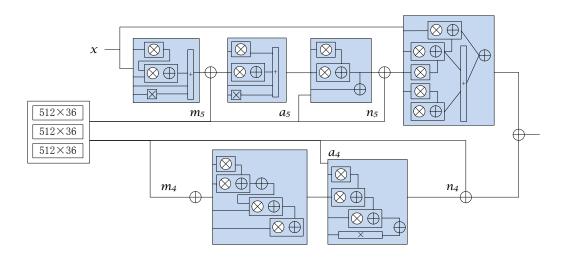

| 7.7 | Schematic of $5^{th}$ degree polynomial evaluator using proposed method | 65 |

| A.1 | Schematic of multipliers for three splits input                         | 78 |

| A.2 | Schematic of squarers for input larger than 53 bits                     | 79 |

| A.3 | Schematic of $53 \times 53$ bit squarer                                 | 80 |

| A.4 | Schematic of 3:1 compressor using two LUTs                              | 82 |

## List of Tables

| 2.1 | Latency and hardware macro count for evaluating $5^{th}$ degree polynomials  |    |

|-----|------------------------------------------------------------------------------|----|

|     | using Horner's Rule.                                                         | 13 |

| 2.2 | Latency and hardware macro count for evaluating $5^{th}$ degree polynomials  |    |

|     | using Dorn's method                                                          | 15 |

| 2.3 | Latency and hardware macro count for evaluating $5^{th}$ degree polynomials  |    |

|     | using Estrin's method                                                        | 16 |

| 5.1 | Latency for evaluating $5^{th}$ degree polynomials using proposed method vs. |    |

|     | conventional methods                                                         | 34 |

| 5.2 | Hardware macro count for evaluating $5^{th}$ degree polynomials using pro-   |    |

|     | posed method vs. conventional methods                                        | 34 |

| 5.3 | Hardware macro count for evaluating $5^{th}$ degree polynomials using alter- |    |

|     | native equation vs. proposed methods                                         | 37 |

| 6.1 | DSP block usage for all methods                                              | 48 |

| 7.1 | Coefficient table for $5^{th}$ degree polynomial evaluator                   | 55 |

| 7.2 | DSP count for each multiplication for $5^{th}$ degree polynomial evaluator   | 55 |

| 7.3 | Coefficient table for $4^{th}$ degree polynomial evaluator                   | 56 |

| 7.4 | DSP count for each multiplication for $4^{th}$ degree polynomial evaluator   | 56 |

| 7.5 | DSP count for each multiplication for $5^{th}$ degree polynomial evaluator   |    |

|     | using Estrin's method                                                        | 60 |

| 7.6  | DSP count for each multiplication for $4^{th}$ degree polynomial evaluator        |    |

|------|-----------------------------------------------------------------------------------|----|

|      | using Estrin's method                                                             | 61 |

| 7.7  | Coefficient table for $5^{th}$ degree polynomial evaluator using proposed method. | 64 |

| 7.8  | DSP count for each multiplication for $5^{th}$ degree polynomial evaluator        |    |

|      | using proposed method                                                             | 64 |

| 7.9  | Coefficient table for $4^{th}$ degree polynomial evaluator using proposed method. | 65 |

| 7.10 | DSP count for each multiplication for $4^{th}$ Degree Polynomial Evaluator        |    |

|      | using Proposed Method                                                             | 66 |

| 7.11 | Hardware resource for $5^{th}$ degree polynomial evaluator                        | 66 |

| 7.12 | Hardware resource for $4^{th}$ degree polynomial evaluator                        | 67 |

| 7.13 | Equivalent LUT count for polynomial evaluators                                    | 68 |

| 7.14 | Performance for $5^{th}$ degree polynomial evaluator                              | 68 |

| 7.15 | Performance for $4^{th}$ degree polynomial evaluator                              | 68 |

| A.1  | Post place and route hardware resource for all types of squarers                  | 81 |

## List of Code

| A.1 | Source code to define evaluation error for Horner's Rule    | 83 |

|-----|-------------------------------------------------------------|----|

| A.2 | Source code to compute evaluation error for Estrin's method | 84 |

| A.3 | Verification of evaluation error for Estrin's method        | 84 |

| A.4 | Source code to compute evaluation error for propose method  | 85 |

| A.5 | Verification of evaluation error for proposed method        | 86 |

## Chapter 1

### Introduction

### 1.1 Motivation

Polynomials are commonly used in high-performance DSP algorithms to approximate the computation of functions, or to model systems parametrically. They are found inside many basic digital circuits including high-precision elementary functional evaluation circuits [1] and digital filters [2]. In fact, at a system level, many applications such as cryptography [3], speech recognition [4] and communications [5], involve the computation of polynomials.

The problem of polynomial evaluation has been investigated by many researchers, with the main research challenge usually being the speed of computation. The benefit of polynomials is that they only require multiplications and additions for the evaluation. However this does not mean that the computation is simple: High degree polynomial computation usually involve multiple large wordlength multiplications, which are time consuming operations. Therefore it is a common objective to reduce the computation time for polynomial evaluation in low latency applications, either through software or hardware approaches.

Earlier works focus on parallel schemes for software realization [6–13]. The parallelism achievable is highly dependent on the number of processing units available. In fact, most such works present results in terms of trade-off between latency and processing unit

cost. For example, Estrin's [12] method needs  $2\lceil log_2(k+1)\rceil$  steps with  $\lceil k/2 \rceil$  processing units to evaluate a  $k^{th}$  order polynomial. Dorn [13] presents a solution with  $\lceil log_2(k) \rceil$  processing units, where  $\lceil log_2(k) \rceil + \lceil log_2(k+1) \rceil$  steps are needed to finish the computing. Several published solutions are closely tied to specific computer architectures, such as SIMD/MIMD and VLIW hardware, in [10,11].

When software approaches are not able to meet performance requirements, alternative hardware implementations of polynomial evaluation algorithms are attractive, since arbitrary degrees of parallel computation can be easier to achieve. In general, many limitations restrict further improvement in software performance for general purpose processors. For example, processors usually support only a fixed operand wordlength and the number of arithmetic units is capped by the architecture of the processor design. Similarly, memory size and bandwidth or the cache size and register resources are usually limited too. With custom circuits, maximum parallelism can be achieved with lower cost in terms of overall hardware resources. This is partly due to the more flexible word length in the data paths and the fact that a more suitable architecture can be selected or customized. In fact, a number of publications present such approaches, implemented in VLSI [14,15].

Another factor that influences the computation complexity is precision. Algorithms involving polynomial evaluation often have to consider the accuracy of computation. The maximum error in the system can be broken down into two components, namely approximation error and evaluation error [16]. Higher degree polynomials with larger wordlength in applications like functional evaluation are necessary to reduce approximation error. For example, to achieve 14 bits accuracy, a  $5^{th}$  degree polynomial is needed for approximating f(x) = 1/(1+x) within the range of x between (0,1) [17]. A  $5^{th}$  degree polynomial with 64 bit operands is required to approximate the function  $f(x) = log_2(1+2x)$  within the range of x between (0,2) [18]. However, this requirement often significantly increases

the computational complexity and latency. Therefore a certain tolerance of evaluation error may be allowed, and the designer could implement faithful rounding for coefficients, and perform truncation in intermediate computations while controlling the total error. Meanwhile, several other solutions have been proposed in the literature to reduce the complexity of polynomial evaluations based on the approximation requirement. Instead of using mathematical algorithms to evaluate polynomials, table based methods are fast and easy, and have been proposed for low degree polynomials in recent implementation [19]. However, this is only applicable to low precision design: to scale to large operand word length, the table size scales exponentially, which clearly becomes unsuitable for higher degree polynomials. On the other hand, polynomial degree can be reduced by carefully selecting the range to be approximated and the approximation methods [16, 20]. Post processing the coefficients derived from standard approximation methods with faithful precision loss can also simplify the polynomial. [20] presents a method to reduce the coefficient word length needed for polynomial approximation of a particular function, which can reduce the total circuit area by 40% and double the speed. [21] proposes a polynomial with sparse coefficients (several bits fixed to 0) which leads to 40% size reduction.

To satisfy both speed and high-precision computation requirements, reconfigurable hardware is increasingly being considered. In field programmable gate arrays (FPGA), a large amount of flexible hardware resources are available for parallelizing algorithms, with the further advantage of flexibility in the data path wordlength. By contrast, custom circuits are not feasible to be optimized for large range of coefficients on polynomials, as they are not re-programmable. Further more, implementing every polynomial algorithm with a dedicated custom circuit would obviously incur high development and engineering costs. Compared to custom integrated circuits, the cost of FPGA development is much lower, and this remains true even when amortized for moderate manufacturing volumes. Many designs with polynomial evaluation have been implemented in FPGA [17, 22, 23]

and naturally, various methods have been proposed to speed up polynomial evaluation methods in FPGAs [16, 20, 21, 24–26].

However, recent articles have only focussed on complexity reduction when implementing in FPGA. Interestingly, very few articles have described parallel evaluation algorithms implemented on modern FPGAs to boost the speed further and analyse the trade-offs on hardware overhead. To investigate parallel polynomial evaluation algorithm implementation on FPGA, algorithms proposed in the literature has been reviewed, and implemented Estrin's method on FPGA. To summarise the result, Estrin's method implementation yields half of the latency required by Horner's Rule. However, the hardware overhead is large, despite dedicated squarer circuits being used instead of multipliers whenever possible to reduce area. Nevertheless, this inspired the author to find a better optimized algorithm that utilize more squaring circuits in order to reduce the multiplication complexity. The resulting novel algorithm is proposed in Chapter 5.

Since the new algorithm relies on dedicated squaring circuits, the next question obviously concerns how good the squarer could be so as to improve the overall polynomial evaluation circuit.

For higher degree polynomial evaluation, the requirement for computation of a square occurs quite often, usually to calculate various exponential of x. It is common to implement this type of squaring operation using a standard multiplier. This may be for reasons of resource sharing, generalization or simply convenience. However, a dedicated squarer can be significantly faster, consume less power, and be smaller than when a general purpose multiplier is used. In fact dedicated squarers are not only used for polynomial evaluations, but also widely adopted in fixed point computations [27] and in various floating point arithmetic circuits [28–30]. Many techniques have been proposed in the literature to improve the performance of squaring circuits for ASIC solutions [31–34]. In reconfigurable hardware, [35] has presented 22% area savings in terms of configurable

logic blocks with 36.3% shorter delay and 45.6% less power when implement in Xilinx 4052XL-1 FPGA compared to an array multiplier on the same FPGA. With the newer DSP enabled FPGAs, squaring units have also been explored in various articles [36–38]. In order to fulfil the requirement for this work (i.e. an efficient squaring circuit for use within a polynomial evaluator), methods to realize a squarer more efficiently on FPGA have been further investigated and a novel efficient squarer in has been proposed Chapter 6.

### 1.2 Scope Definition

The problem of polynomial evaluation can be summarized as follow. Using a general format for  $k^{th}$  degree polynomial evaluation,

$$f(x) = \sum_{i=0}^{k} a_i x^i$$

(Eq. 1.1)

The fixed point numbers x is defined as the input of the polynomial with a set of coefficients  $a_i$  of constant value. These coefficients can be obtained by various algorithms. In most of the system and within the consideration here, the coefficients will not be changed frequently although they could be updated from time to time. In other words, a system for which the *computation using* fixed  $a_i$  is the limiting factor, rather than the *computation of*  $a_i$  will be considered only.

Although the coefficients can be modified due to different approximation accuracy requirements or different ranges of input x, one particular set of coefficients could be used for long strings of different input x and do not change frequently with respect to the data in most of system implementations [15]. Such a system that could fulfil the requirement is commonly used in many applications, thus the discussion here is meaningful.

The range of the coefficients and the input x is defined to be [0,1]. This is mainly for the ease of accuracy analysis performed later.

### 1.3 Contributions

### 1.3.1 Novel Polynomial Evaluation Algorithm

We propose a novel algorithm in this thesis to address the problem of polynomial evaluation in a fast manner with low hardware cost. The algorithm parallelizes the evaluation process by grouping different monomials. It then transforms each group into its vertex format which trades multiplication with square and utilizes the dedicated squarer to reduce the hardware cost. The result in this thesis shows that it is able to achieve short latency while maintaining minimum hardware cost. The general form of the novel design has been provided as well.

## 1.3.2 Comparison of Fixed Point Polynomial Evaluation Algorithms Implementation on FPGA

We implement the novel algorithm in FPGA as well as two algorithms from the literature to compare the performance and hardware utilization using two real applications. The applications are to approximate elementary functions. In the comparison, only the polynomial evaluation algorithm is different among the three designs and they are designed to fulfil same requirements. We will show the post-place and route results to prove that our theoretical findings, and mathematical analysis are applicable to real designs.

### 1.3.3 Novel Integer Squarer Design on FPGA

We have proposed a dedicated squarer design for implementation on FPGA, not only for our novel polynomial evaluation algorithm but for other uses as well. The design uses fewer DSP blocks while trading DSP blocks with limited hardware overhead, and shows better efficiency in terms of overall hardware utilization in the FPGA than competing designs. Considering DSP blocks are limited in modern FPGAs, the novel design is useful to reduce the overall DSP blocks usage and enable larger designs on single FPGA, while not demanding excessive amounts of additional logic.

### 1.4 Organization of the Thesis

Below is the organization of this thesis.

In Chapter 2, polynomial evaluation algorithms in the literature will be analyzed and various optimization methods proposed in recent work are described and discussed.

In Chapter 3, modern FPGA architectures are reviewed and multipliers based on these features are discussed.

In Chapter 4, conventional squarer designs and their FPGA implementation are presented.

In Chapter 5, the novel polynomial evaluation algorithm is proposed and is compared with the algorithms in the literature.

In Chapter 6, a novel squarer design is proposed, along with FPGA implementation details, and its performance will be compared with conventional designs.

In Chapter 7, the novel polynomial evaluation algorithm is implemented for real applications, and compared with conventional algorithms operating under the same conditions.

Chapter 8 concludes the thesis with discussion on possible improvements that could be considered in future.

## Chapter 2

# Conventional Polynomial Evaluation Algorithms, Implementation and Optimization

### 2.1 Polynomial Evaluation Algorithms

Polynomial evaluation procedures have been the subject of investigation since the 1950s. Mainly based on alternative computer architectures, many different software approaches have been proposed in the literature to optimize or accelerate the evaluation process. Most of the research focuses on the trade-off between general purpose processing units and system-level parallelism. A few prominent methods which have been published previously are presented and discussed below.

### 2.1.1 Direct Method

Directly computation of polynomials is by far the simplest method to describe. This involves computing exponentials of x (i.e.  $x^i$  in the general form) and multiplying each power with the corresponding coefficient  $a_i$ . This is most often used for low degree polynomial evaluation [39]. The computing process can be highly parallel, if the resources permit, but the total number of steps to complete the computation is large. More specifically, that a large number of multiplications are required. Meanwhile, the resultant

accuracy is relatively low [17]. Therefore it is much less commonly used for higher degree polynomials.

### 2.1.2 Horner's Rule

Horner's Rule is the most basic and common rule for computing polynomials. It was developed in the very early days of computation and it is widely used in numerous complex applications [40, 41]. Horner's Rule has been proven by Pan [6] and Winograd [22] to involve the minimum number of steps to evaluate a particular polynomial, i.e. it is optimum in terms of computational steps. Furthermore, it also has a regular structure which is easy to be implemented. All these factors lead to widespread adoption of the methods since it was invented. The rule involves the transformation of the polynomial into a series of multiply-adds. Considering the polynomial equation stated in (Eq. 1.1), Horner's Rule re-writes the formula into

$$f(x) = \{ \dots ((a_k \cdot x + a_{k-1}) \cdot x + a_{k-2}) \cdot x + \dots + a_0 \}$$

(Eq. 2.1)

One multiply-add unit is used to compute  $a_i \cdot x + a_{i-1}$  and this can be reused recursively to complete the overall computation. Therefore, it is an ideal method for processors containing multiply-add arithmetic (or multiply-accumulate) units. However, Horner's Rule is inherently a serial process and consequently the critical path for this method is long.

### 2.1.3 Parallel Methods

For low latency designs, especially in communication or cryptography applications, parallel processing is desirable. A few such methods are suitable for these applications with specific computer architectures. Dorn [13] proposes a generalized form of Horner's rule, which can be applied on general computing architectures which have more than one computational unit. For a  $k^{th}$  degree polynomial, this method can reach a  $n^{th}$  degree parallelism, where  $n \leq \lceil log_2(k) \rceil$ . The general format is,

$$f(x) = \sum_{m=0}^{n-1} p_m \cdot (x^n) \cdot x^m$$

(Eq. 2.2)

where

$$p_m(x) = \sum_{i=0}^{\log_2 k} a_{m+jn} \cdot x^j$$

(Eq. 2.3)

The latency boost for Dorn's method is obvious. Compared to the original Horner's Rule, approximately 1/n the amount of evaluation time is needed, and the only serial process involved is to calculate the power of x. The trade-off of this method is circuit area, with hardware requirements naturally depending upon the degree of parallelism. In Dorn's original paper, the parallelism that the system can achieve is based on the available number of processing units.

Another well-known method which parallels the evaluation process was proposed by G. Estrin in 1960 [12]. In his famous paper discussing the future of computer system architecture, he presented a method with a sequence that uses multiple multipliers to increase the speed of function evaluation. The general format reformed after (Eq. 1.1) could be shown as below

$$f(x) = \sum_{i=0}^{n} (a_{2i+1}x + a_{2i}) \cdot x^4 + (a_{2n+2} \cdot x^{2n+2}) \cdot (k - 2n - 1)$$

(Eq. 2.4)

where  $n = \lfloor k/2 \rfloor$ . An implementation of computer architecture for this algorithm was presented in the original paper as well (details of it can be found in the graph given in the appendix [12]). Each sub-sequence can occupy one processor and another processor can be used to evaluate the powers of x. The proposed architecture can complete the computation within  $2\lceil log_2(k+1) \rceil$  steps. Obviously the main trade-off is also the hardware cost. To achieve the maximum level of parallelism,  $\lceil k/2 \rceil$  processors are needed

for Estrin's design. This has been used by various applications [17, 42] for fast parallel evaluation of polynomials.

Other than the two methods mentioned above, tree structures approaches have been presented in previous works [7–9]. These methods are discussed in the content of ultra higher degree polynomial computation. Different folding schemes are used to find the maximum degree of polynomial that could be evaluated by a particular given method in a certain number of steps with the aim being to achieve the minimum number of steps required to evaluate a polynomial. Thus, when a higher degree polynomial is broken into smaller segments, the sub groups still follow the folding scheme that can fully utilize the schemes capability. Tables are shown in the original articles of such degrees that individual schemes could achieve, but which are not included here due to limited space. As these methods only tend to manifest their advantages for polynomials of degree greater than 20, they are not the main comparison reference in this thesis and thus it is not going to discuss further details on these methods.

Some previous works have also presented designs targeting alternative computer architectures for specific purposes. For example, special grouping schemes are presented in [10] based on MIMD and SIMD computers. In [11], polynomials are evaluated using a modern multimedia processors with a MAC unit and parallel execution scheduling. As they are optimized for a particular architecture rather than being generalised, they are also not considered in this thesis.

### 2.2 Polynomial Evaluation Implementation

Polynomial evaluations are not only implemented in software, which is limited by the computer architecture. Many hardware approaches also adopt similar methods when building application specific circuits. Horner's Rule is widely used in many hardware designs [20, 43]. Dorn's method has been implemented by Burleson [15] in ASIC, where

arithmetic units are not limited by architecture. For the sake of comparison, simplified circuit diagrams will be used here to illustrate Horner's Rule, Dorn's method and Estrin's method. The circuit is broken down into macro blocks of multiplier, squarer and adder. Area and performance metric of polynomial evaluation algorithms will be discussed on the level of these macro blocks. As processing resources are virtually unlimited in custom circuits, only the maximum degree of parallelism of a certain method is going to be considered. A  $5^{th}$  degree polynomial is used as an example, which can be written as

$$f(x) = a_5 \cdot x^5 + a_4 \cdot x^4 + a_3 \cdot x^3 + a_2 \cdot x^2 + a_1 \cdot x + a_0$$

(Eq. 2.5)

and this will also be used to compare against the proposed method later. Meanwhile, for the purpose of performance comparison in theory, a few assumptions are made below.

**Assumption 1** Define the following Macros used in theoretical comparison of polynomial evaluation,

$Parallel\ multiplier$   $M_{mul}$   $Parallel\ squarer$   $M_{sq}$   $Carry\ propagate\ adder$   $M_{add}$

and these Macros have the following properties:

$$T_{mul} > T_{sq} >> T_{add}$$

$$A_{mul} >> A_{sq} >>> A_{add}$$

In the assumption,  $T_{mul}$  is defined as the latency for an optimum pipelined parallel multiplier and  $T_{add}$  is defined as the latency of an optimum pipelined adder.  $T_{sq}$  will be the notation for the latency of an optimum pipelined parallel squarer, and which should ideally be lower than that of  $T_{mul}$ . A will be the notation used to describe the area of an individual macro and the a parallel multiplier is much lager than a parallel squarer in similar architecture. Obviously, the adder is the smallest and fastest macro among three.

### 2.2.1 Horner's Rule

Using Horner's Rule, the polynomial in (Eq. 2.5) can be transformed into,

$$f(x) = ((((a_5 \cdot x + a_4) \cdot x + a_3) \cdot x + a_2) \cdot x + a_1) \cdot x + a_0$$

(Eq. 2.6)

The evaluation process for implementing (Eq. 2.6) can be illustrated in the graph shown in Figure 2.1. In Figure 2.1 and subsequent figures of circuit diagram for polynomial

Figure 2.1: Diagram for evaluating  $5^{th}$  degree polynomials using Horner's Rule.

evaluation, sequential operators will be denoted from left to right, and dependences denoted with arrows. Using Horner's Rule, 10 steps of computation are needed, which are namely five multiplications followed by five additions each. As there is no parallel execution, the latency of the evaluation largely depends upon how well the multiplier and adder have been designed. The overall latency using Horner's rule is  $5 \cdot (T_{mul} + T_{add})$ . Although, through proper pipelining, the multiplication and the addition can reach high throughput with a fast system clock rate, the latency is still relatively long due to the existence of longer pipeline stages. Table 2.1 summarizes the implementation details for Horner's Rule

| Latency                       | Multiplier | Adder |  |

|-------------------------------|------------|-------|--|

| $5 \cdot (T_{mul} + T_{add})$ | 5          | 5     |  |

Table 2.1: Latency and hardware macro count for evaluating  $5^{th}$  degree polynomials using Horner's Rule.

### 2.2.2 Dorn's Method

Dorn's method can be used to achieve  $3^{rd}$  degree parallelism on the same polynomial. The format of Dorn's equation to achieve this is shown below,

$$f(x) = (a_2 + a_5 x^3) \cdot x^2 + (a_1 + a_4 x^3) \cdot x + (a_0 + a_3 x^3)$$

(Eq. 2.7)

The whole equation can be subdivided into three subexpressions which can be computed in parallel. The cube of x can be shared among all three subexpressions and thus should be computed upfront. It is obvious that the evaluation process is more complex than Horner's Rule (and in general the additional complexity grows with polynomial order). The evaluation process can be summarized in Figure 2.2 which shows that 12 steps are necessary, of which 2 steps are needed to compute  $x^3$ , 6 steps in parallel compute the three subexpressions, 2 steps are used to multiply with the respective power of x for the first two subexpressions, and 2 steps to sum all three parts together. Note that the last addition has to wait for both operands to be ready. With some degree of parallelism where the help of dedicated squarer, the latency of Dorn's method is shorter, but it is at the expense of additional hardware overhead. When this is implemented, the hardware

Figure 2.2: Diagram for evaluating  $5^{th}$  degree polynomials using Dorn's method.

resource summary is as shown in Table 2.2, where one squarer and one multiplier is

for  $x^3$  (although one may argue a dedicated cubic operator could also be used in this case, it is outside the scope of discussion in this thesis), three multipliers followed by three adders are for three subexpressions, one multiplier is to multiply x with the second subexpression, one multiplier is to multiply  $x^2$  with the first subexpression and two adders are for the final addition.

| Latency                                      | Multiplier | Squarer | Adder |

|----------------------------------------------|------------|---------|-------|

| $T_{sq} + 3 \cdot T_{mul} + 3 \cdot T_{add}$ | 6          | 1       | 5     |

Table 2.2: Latency and hardware macro count for evaluating  $5^{th}$  degree polynomials using Dorn's method.

### 2.2.3 Estrin's Method

The converted format for the same polynomial using Estrin's method is,

$$f(x) = (a_5 \cdot x + a_4) \cdot x^4 + (a_3 \cdot x + a_2) \cdot x^2 + (a_1 \cdot x + a_0)$$

(Eq. 2.8)

Similar to Dorn's method, three subexpressions of the equations are able to be computed individually by one multiplier followed by one adder. Another two multipliers with two adders are used to multiply subexpressions with power of x and sum them together. However, different from Dorn's method, the even powers of x should be computed first, i.e.  $x^2$  followed by  $(x^2)^2$ , which shall be implemented using two squarers. The total number of evaluation steps is still 12 but it has a shorter latency than Dorn's method. The critical path, is determined by the first subexpression in (Eq. 2.8). It contains the path of two squaring and one multiplication, which is longer than the other two paths in parallel. The evaluation process can be summarized graphically as shown in Figure 2.3 and the critical path is shown in bold arrow. The amount of hardware resource is given in Table 2.3. Estrin's method yields an improvement over Dorn's method in terms of latency at the same hardware cost and it will be selected as the parallel evaluation method to be compared with proposed method later.

Figure 2.3: Diagram for evaluating  $5^{th}$  degree polynomials using Estrin's method.

| Latency                              | Multiplier | Squarer | Adder |

|--------------------------------------|------------|---------|-------|

| $2 \cdot T_{sq} + T_{mul} + T_{add}$ | 5          | 2       | 5     |

Table 2.3: Latency and hardware macro count for evaluating  $5^{th}$  degree polynomials using Estrin's method.

### 2.3 Polynomial Evaluation Optimization

With the flexibility of hardware circuits, designers are able to not only build the evaluation circuit with custom arithmetic operators, but also customize the polynomial evaluation based on the precision requirement and available hardware components (such as implementation in FPGAs). In function approximation, procedures to derive an optimized polynomial have been proposed [16]. The framework, involving range reduction and bit-width optimization, is able to produce a design with simplified polynomials. [20] and [43] have presented similar methodologies, which focus on reducing the complexity of the polynomials as well.

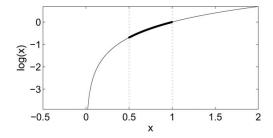

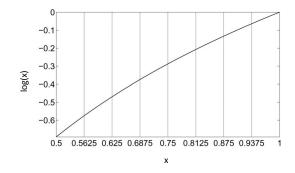

The degree of polynomial used to approximate the function is largely determined by the range of the function and it directly links to the area, latency and throughput of the overall design. It is shown that the area could be half and the latency could be only 1/10 when range reduction is performed [16]. On the other hand, if designs have to be approximated across the whole range, sub-intervals could be divided. Although more memory might be needed for breaking down into segmented ranges, it could significantly reduce the degree required for the same precision [26]. Figure 2.4 shows the function before and after range reduction optimization and Figure 2.5 illustrats how the sub-intervals are formed.

Figure 2.4: Function with range reduction

Figure 2.5: Function with sub-intervals

Rounding the coefficients to the nearest sweet spot numbers within the bound of evaluation error allowance is another way to simplify the evaluation process. It is obvious that custom adders and multipliers would be more efficiently fit with these rounded coefficients, rather than general purpose arithmetic units. Other coefficient optimization methods, like in [21,25], have been proposed to make the multiplier smaller with more '0's inside the multiplier operand, which could make one or more rows of partial products in

the multiplier to be constant '0' and therefore size of multiplier can be shrunk to increase the speed as well as to reduce area.

As design automation is used in these frameworks, the processing time to generate polynomial evaluator is negligible compared to the computation of constrained approximation [43]. What's more, the process is usually performed once for a particular polynomial and the results can be reused over and over (at least until the underlying FPGA or implementation architecture changes). Therefore, it is often worthwhile to use these methods to simplify the polynomial evaluation problem, if they are able to map to the required architecture.

## Chapter 3

# Conventional Arithmetic Implementation on FPGA

### 3.1 FPGA Background

Field Programmable Gate Array (FPGAs) are semiconductor devices that are based around a matrix of configurable logic blocks (CLBs) connected via programmable interconnects [44]. In general, FPGAs are more flexible than ASICs as they are able to programmed easily to desired functions or applications, with the emphasis on the ease of reprogrammability. This is the feature that makes such devices suitable for building processing units for polynomials which are likely to have to adapt to parameter changes from time to time. The fundamental building block of an FPGA is its logic cells. Despite the different hardware used to realize the logic cell functions, and different input widths provided by various FPGA vendors, they can be mapped to certain logic functions with the help of the synthesis and mapping tools. Xilinx Virtex-4 FPGA cells contain a 4 input look up table (LUT), which can also be used for RAMs or as shift registers [45]. While in more recent Virtex-6 and 7 series FPGAs, 6 inputs LUTs are provided, to give more flexibility [46]. Other than the LUT, multiplexers, flip flops and carry chains are available as basic items of reconfigurable hardware. A typical CLB that contains all these basic elements is shown in Figure 3.1. Altera provide similar architectures in their basic

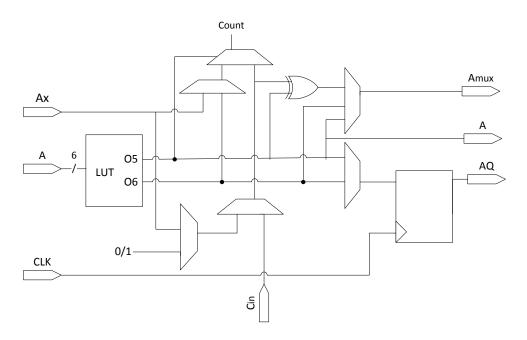

Figure 3.1: Simplified diagram of LUT, multipliexer, flip flops and carry chains in CLB in Xilinx Virtex 6 FPGA.

reconfigurable blocks, although they are based on 4 input LUTs. In order to interconnect the CLBs with each other, interconnect blocks have been designed to route different blocks, and these are programmed automatically by place and route tools.

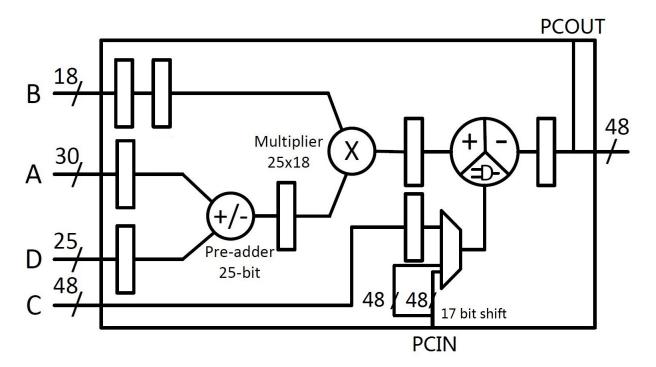

In recent modern FPGA architectures, more functional blocks are added to optimize applications. Reconfigurable DSP blocks enable fast digital signal processing. In the Virtex 6 architecture they contain a 25×18 bit signed multiplier with a programmable ALU following its multiplication data path [47]. This extension of wordlength is an improvement from the DSP blocks found in Virtex 4 and previous devices, and was first supported in the Virtex 5. The simplified DSP48E1 block diagram is shown in Figure 3.2. The DSP block includes an optional pre-adder at one of its inputs. The ALU unit can be programmed as a 48 bit adder, which can accumulate the multiplier product and the adjacent DSP result through the dedicated 48 bit routes in a single clock cycle. The dedicated routes are from the PCOUT ports of the adjacent DSP to the PCIN ports of the current one. This bus also has an option to perform a 17 bit right shift. The

input of the adder can be the 48 bit number from input C with an optional associated CARRYIN, but it is mutually exclusive with the PCIN signals. The DSP48E1 has also includes internal pipeline registers, allowing it to run at a frequency of up to  $450\,\mathrm{MHz}$  (for -1 speed grade Virtex 6 devices) [47]. However, as DSP blocks are combined for larger operands, further pipelining is required, which is implemented using LUTs and flip flops in the Slices.

Figure 3.2: Simplified diagram of DSP48E1 in Xilinx Virtex 6 FPGA.

Block RAM has also been included in modern FPGAs to enable large memory implementations. Each RAM block, named RAMB36E1 in the current device, is 36Kb in size and can be configured as  $64K\times1$ ,  $32K\times1$ ,  $16K\times2$ ,  $8K\times4$ ,  $4K\times9$ ,  $2K\times18$ ,  $1K\times36$  or  $512\times72$ . Both read and write operations require one clock cycle.

### 3.2 Parallel Multiplier in FPGA

### 3.2.1 Multiplier Based on LUT

The architecture of parallel multiplier involves partial product generator and adder tree. For example, a  $4\times4$  bit parallel multiplier with inputs a and b will first generate 16 partial products shown in Figure 3.3.

The partial product array could be reduced using adder tree into one row of sum and one row of carry, which could be added using carry propagate adder at last. Parallel

Figure 3.3: Partial product alignment of  $4\times4$  bit parallel multiplier.

multipliers have been explored for many years and thousands of designs have been implemented in hardware. Booth encoding schemes, Wallace tree [48], Baugh and Wooley's method [49] and many more algorithms have been introduced to do fast parallel multiplication in custom circuits. These circuits can be implemented in FPGAs with little difficulty, even without specialized DSP functional block being provided. Several works have proposed multiplier designs purely using LUTs in [50,51].

### 3.2.2 Multiplier Based on Cascaded Chains of DSP Blocks

In modern FPGAs where DSP blocks are available, multiplication can utilize these functional blocks to reduce latency, rather than relying on LUTs. The cascaded chain through dedicated routes allows users to build large wordlength multipliers running at high speed. This decomposition is as follows: take a  $35\times35$  bit multiplication  $x\cdot y$  as an example.

Figure 3.4: Pipeline schematic of general purpose multiplier.

Each of the inputs can be split into two sub operands with smaller wordlength:

$$x = a_0 + a_1 \cdot 2^{17} \tag{Eq. 3.1}$$

$$y = b_0 + b_1 \cdot 2^{17} \tag{Eq. 3.2}$$

Therefore, the full multiplication can be re-written as,

$$x \cdot y = a_0 b_0 + (a_1 b_0 + a_0 b_1) \cdot 2^{17} + a_1 b_1 \cdot 2^{34}$$

(Eq. 3.3)

which contains four sub products. Note that each operand in these four sub multiplications is equal to or less than 18 bits (17 bits unsigned numbers for lower splits  $a_0$  and  $b_0$  and 18 bits two's complement signed numbers for the most significant parts  $a_1$  and  $b_1$ ). After the sub multiplications are computed, the products can be added through the post-adder, one by one, within 4 cycles. No extra LUTs are needed for the addition in this case. Figure 3.4 shows a detailed implementation.

As either  $a_1$  or  $b_1$  can be at most 25 bits in size, if an operand exceeds 35 bits, for example 42 bits, then  $a_1b_1$  is not able to fit within one DSP and  $a_1$  must be split into sub operands of 17 bits and 8 bits respectively. In this case, an additional DSP would be chained after the last DSP to perform the multiplication of the 8 msbs of  $a_1$  with  $b_1$ .

When the wordlength is greater than 43 bits, further splits are required to complete the addition, and correspondingly more clock cycles being needed to obtain the result. For a given wordlength w where k splits are needed, the number of DSP blocks needed for a standard multiplier is:

$$f(k) = \begin{cases} k^2 & \text{if } w - 17k > 1\\ k^2 + 1 & \text{if } w - 17k \le 1 \end{cases}$$

(Eq. 3.4)

It can be seen that, as the wordlength increases, the number of DSP blocks required by the multiplier grows quadratically. We will revisit this point later when demonstrating that it is much more efficient to perform squaring using a specialized squarer, especially as wordlength becomes large. This will be discussed more fully in Chapter 4.

The standard cascaded method has been provided as a IP core from Xilinx CoreGen. It has been optimized to run at the maximum speed of the DSP, however, it is limited to a maximum wordlengh of 64 bits.

### 3.2.3 Multiplier with Fewer DSP Blocks

For complex and computationally intensive algorithms, large multipliers could be designed with fewer DSPs. One method is to use Karatsuba-Ofman algorithm [52]. Classic Karatsuba-Ofman algorithm reduces the multiplier complexity by exchanging multiplication with addition and it was extended by [36] to reduce DSP blocks usage for multiplier. A two split example is shown as,

$$x \cdot y = a_1 \cdot b_0 + a_0 \cdot b_1$$

$$= a_1 \cdot b_1 + a_0 \cdot b_0 - (a_1 - a_0) \cdot (b_1 - b_0)$$

(Eq. 3.5)

Noted that three multiplications, instead of four are needed in (Eq. 3.5). It is reported in [36] that it could reduce the DSP blocks usage from 4 to 3 in a  $34 \times 34$  bit multiplier at the cost of 68 additional LUTs and from 9 to 6 in a  $52 \times 52$  bit multiplier at the cost of 312 additional LUTs.

The other method, which is more efficient, is to arrange the DSP in the form of "tiling" where 25 bits input is available in DSP blocks. [36] has also reported a  $58 \times 58$  bit multiplier with 8 DSP blocks and 388 LUTs where non-standard tiling arrangement of DSP blocks is used. Due to the special tiling arrangement, asymmetric DSP blocks are fit into the  $58 \times 58$  bit operand with only one small multiplier in the middle which must be implemented using LUTs. The diagram of such method is shown in Figure 3.5. In fact, there are many variations of "tiling like" multiplier design where operands of the multiplier are not equal. When this happens, for example a  $48 \times 34$  multiplier, can easily be mapped to four DSP blocks, by dividing 48 bits into 24 + 24 bits and dividing 34 bits into 17 + 17 bits. Noted that with the tiling arrangement, it is not simple to chain the

Figure 3.5: Tiling multiplier example

DSPs through dedicated routes and the adders are then implemented in LUTs.

More recently [53,54] have proposed advanced usages of such asymmetric DSP blocks in building large multipliers. They are none-pipelined design and thus not suitable for polynomial evaluators running in high speed.

## Chapter 4

## Conventional Squarer Design

It is common to implement a squaring operation using a standard multiplier. This may be for reasons of resource sharing, generalization or simply convenience. According to (Eq. 3.4), it is much more efficient to perform squaring using a specialized squarer when multiplier grows quadratically as wordlength increases The computation of a square is required in many DSP algorithms and thus for high performance applications, specialized hardware for squaring may be desired. A dedicated squarer can be significantly faster, consume less power, and be smaller than a multiplier and therefore they are widely adopted in fixed point function evaluation [27] or in various floating point arithmetic computations [28–30].

## 4.1 Squarer Designed for ASICs

In theory, a squarer can reduce the number of partial products by half compared to a parallel multiplier, as both inputs are the same. For example, Figure 4.1 can be easily dervied from Figure 3.3 with identical partial products identified in bold and thus they can be added with one bit left shift. There are many variations of squarer design proposed in the literature. In [51], 40% area reduction and 18.6% speed improvement is achieved compared to the multiplier in ASIC, which applies the folding of partial products (which can be seen in Fig. 4.1). Several other squarer designs have been reported to have even

|          |           |               | $a_3$         | $a_2$         | $a_1$         | $a_0$     |

|----------|-----------|---------------|---------------|---------------|---------------|-----------|

|          |           |               | $a_3$         | $a_2$         | $a_1$         | $a_0$     |

|          |           |               | $a_3a_0$      | $a_2a_0$      | $a_1a_0$      | $a_0 a_0$ |

|          |           | $a_3a_1$      | $a_2a_1$      | $a_1a_1$      | $a_0a_1$      |           |

|          | $a_3a_2$  | $a_2a_2$      | $a_1a_2$      | $a_0a_2$      |               |           |

| $a_3a_3$ | $a_2a_3$  | $a_1a_3$      | $a_0a_3$      |               |               |           |

| $a_3a_3$ |           | $a_2a_2$      | $2a_{0}a_{3}$ | $a_1a_1$      |               | $a_0a_0$  |

|          | $2a_2a_3$ | $2a_{1}a_{3}$ | $2a_{1}a_{2}$ | $2a_{0}a_{2}$ | $2a_{0}a_{1}$ |           |

Figure 4.1: Partial product alignment of  $4 \times 4$  parallel squarer.

higher area reductions as well as speed improvements for ASIC solutions [31–33, 55]. In the context of FPGA implementation, [35] has reported a squarer with Wallace-tree and carry-select adder that requires 22% less LUTs, is 36.3% faster and enjoys a 45.6% power saving on Xilinx 4052XL-1 FPGA compared to a generalized multiplier.

### 4.2 Squarer Based on Cascaded Method

In a DSP enabled FPGA, it is more efficient to build squarers using DSP blocks wherever possible. A straightforward method for building large wordlength squaring circuits in FPGA is by cascading DSPs as is briefly discussed in [36]. For squaring, x and y are identical thus (Eq. 3.3) becomes:

$$x \cdot x = a_0^2 + (a_1 a_0 + a_0 a_1) \cdot 2^{17} + a_1^2 \cdot 2^{34}$$

(Eq. 4.1)

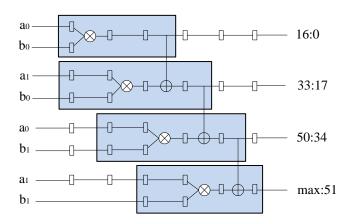

Since the middle two terms in the bracket are the same, their summation can be simplified to a one bit left shift. The alignment of DSP blocks shown in Figure 4.2 acheives this, and has a similar pipeline to the general purpose multiplier. This alignment allows a DSP block to be eliminated compared to using a standard multiplier – and as the wordlength increases, more DSPs can be saved. Equations (Eq. 4.2) and (Eq. 4.3) below show that using this method, only 6 and 10 DSPs are needed for three splits and four splits operands respectively. This compares to 9 and 16 DSPs required, respectively, for

Figure 4.2: Pipeline schematic of squarer based on cascading DSP chains.

the general purpose CoreGen multiplier.

$$x \cdot x = a_0^2 + 2a_1a_0 \cdot 2^{17} + (a_1^2 + 2a_2a_0) \cdot 2^{34}$$

$+ 2a_2a_1 \cdot 2^{51} + a_2^2 \cdot 2^{68}$  (Eq. 4.2)

$$x \cdot x = a_0^2 + 2a_1 a_0 \cdot 2^{17} + (a_1^2 + 2a_2 a_0) \cdot 2^{34}$$

$$+ (2a_2 a_1 + 2a_3 a_0) \cdot 2^{51} + (a_2^2 + 2a_3 a_1) \cdot 2^{68}$$

$$+ 2a_3 a_2 \cdot 2^{85} + a_3^2 \cdot 2^{102}$$

(Eq. 4.3)

We can derive a similar equation to (Eq. 3.4) for the DSP count required for this method with w bits split into k parts as given in (Eq. 4.4). Note that the relationship between w and k is slightly different to that defined for the multiplier, for example, four splits are needed for 59 bits instead of three.

$$f(k) = \begin{cases} (k^2 + k)/2 & \text{if } w - 17k > 1\\ (k^2 + k)/2 + 1 & \text{if } w - 17k \le 1 \end{cases}$$

(Eq. 4.4)

In common with the multiplier, all the additions for the above squarer design lie within the boundary of DSP blocks so the only circuit elements outside the DSP blocks are the pipeline registers.

A similar rationale was used in [36] (targeting the Xilinx Virtex 4) for the FloPoCo project [30]<sup>1</sup>. We have mapped the auto-generated FloPoCo squarer to the Virtex 6

<sup>&</sup>lt;sup>1</sup>FloPoCo version 2.4.0, http://flopoco.gforge.inria.fr/

FPGA for comparison purposes. However, we have not been able to produce expected performance using ISE v13.4 as the design is not optimally pipelined for the newer DSP architectures. Hence, in the course of our work, we have also rewritten an optimized design for FloPoCo, based on the same decomposition and design principles, that we refer to as the "cascaded method". The implementation results of original FloPoCo and the cascaded method will be presented in Section 4 where they are compared to the novel method developed during the course of this research. We have adopted and extended this method to the Virtex 6 FPGA, yielding good results (which will be discussed later in Chapter 6).

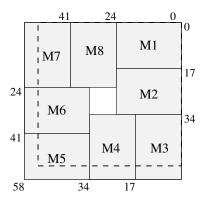

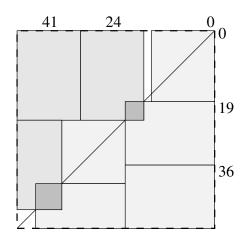

## 4.3 Squarer Based on Non-standard Tiling Method

The cascaded method is a simple approach to build squaring circuits, but it still uses a larger number of DSP blocks than is necessary. To further reduce DSP usage, the tiling method [36] was proposed, applied to Xilinx Virtex 5 or newer FPGA devices where 25×18 bit DSP blocks are supported. The main approach is to achieve efficiency gains through maximizing the utilization of the asymmetrically sized DSP inputs. This is similar to what has been proposed for the multiplier in Chapter 3. Two different tiling methods were suggested for squaring circuits optimized for 53-bit operands; one of them can reduce the number of DSPs from 6 (cascaded method) to 5. Figure 4.3 shows the alignment of the 5 DSPs required to complete the square in this method. The main drawback to this approach is the potentially high LUT usage, as there are four small multiplications that must be implemented (two are shown in white in the middle top and bottom left, and two in dark grey colour). As pointed out by the original author of [36], "It is expected that implementing such equations will lead to a large LUT cost, partly due to the many sub-multipliers, and partly due to the irregular weights of each line (no 17-bit shifts) which may prevent optimal use of the internal adders of the DSP48E blocks." [36].

Figure 4.3: Tiling method for square

Although he did not provide full implementation details, we have reproduced the design based on Figure 4.3, which applies to operand widths between 43 and 53 bits, to compare with the other methods evaluated.

## Chapter 5

# Novel Polynomial Evaluation Algorithm

In this chapter, a novel polynomial evaluation algorithm is proposed. It involves transformation of the general form of polynomial into "square rich" format. The main benefit of the algorithm is to achieve high level of parallelism with minimum hardware cost. Although the total steps will be more than those used for Horner's Rule, the implementation in hardware will be even smaller than the "optimum method in theory", thanks to the efficiency gains in the use of squarer units. The latency of this method is similar to Estrin's method as described in the literature but uses much less hardware resource than the highly paralleled method. The algorithm can be applied to polynomials of arbitrary degree.

### 5.1 First Hypothesis

The novel method is based on the hypothesis below, beginning with a  $2^{nd}$  degree example.

**Hypothesis 1** To evaluate the following 2nd order polynomial,

$$f(x) = \sum_{i=0}^{2} a_i x^i$$

(Eq. 5.1)

it is advantageous to use,

$$f(x) = a_2 \cdot ((x + m_2)^2 + n_2)$$

(Eq. 5.2)

to evaluate the polynomial.

The new format completes the square and converts the original polynomial into its vertex form. In this equation (Eq. 5.2)  $m_2$  and  $n_2$  are coefficients derived from  $a_1$  and  $a_0$ , thus they are considered as being known values. Therefore, four steps are needed to compute (Eq. 5.2), which are one addition, one squaring followed by another addition, and a final multiplication. The same number of steps are needed if Horner's Rule is used to compute the  $2^{nd}$  degree polynomial, however, it requires two multipliers and two adders. The advantage of the proposed method is obvious in terms of hardware cost where one multiplier is shrunk to a squarer, even though the total number of steps is the same as for Horner's Rule.

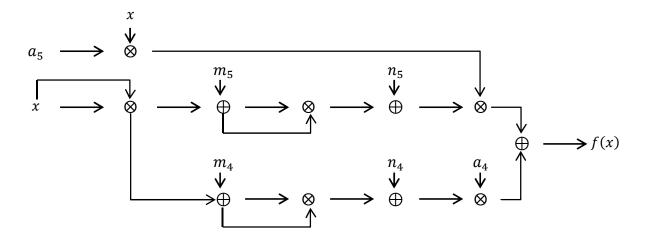

## 5.2 Novel Method Example

The above method can be applied to general polynomial evaluation as will be illustrated in an example for the same  $5^{th}$  degree polynomial in (Eq. 2.5),

Hypothesis 2 A 5<sup>th</sup> degree polynomial which can be expressed as,

$$f(x) = \sum_{i=0}^{5} a_i x^i$$

(Eq. 5.3)

can be evaluated using,

$$f(x) = a_5 \cdot x \cdot [(x^2 + m_5)^2 + n_5] + a_4 \cdot [(x^2 + m_4)^2 + n_4]$$

(Eq. 5.4)

Similar to hypothesis 1,  $n_4$ ,  $n_5$ ,  $m_4$  and  $m_5$  are all considered to be known real values derived from the original coefficient set. To derive the above arrangement of terms, the original polynomial can be divided into two subexpressions,

$$f(x) = x \cdot (a_5 x^4 + a_3 x^2 + a_1) + (a_4 x^4 + a_2 x^2 + a_0)$$

(Eq. 5.5)

If the method in hypothesis 1 is applied to complete the square in each bracket then the equation becomes (Eq. 5.4).

In this equation (Eq. 5.4), the total multiplication can be completed by employing three multipliers and three squarers. To evaluate using the new format,  $x^2$  is calculated first to be shared among both subexpressions and to be added with a coefficient in each subexpression. This is subsequently followed by another square function and by an addition. Meanwhile, the computation of term  $a_5 \cdot x$  should be completed and both subexpressions can then immediately multiply their coefficients. The final addition is performed using one adder. In terms of latency, the novel method could be as fast as  $2 \cdot T_{sq} + T_{mul} + 3 \cdot T_{add}$ . Figure 5.1 shows the evaluation sequence.

Figure 5.1: Diagram for evaluating  $5^{th}$  degree polynomials using proposed method.

Table 5.1 compares the latency with conventional methods. It is shown to be similar to Estrin's Method (only two adders slower and the gap could be smaller in real application), and is much faster than the other two. The effective hardware cost, is summarized in Table 5.2. Compared to five multipliers and five adders used by Horner's Rule, the proposed method involves one more step but can achieve hardware savings if an efficient

| Method          | Latency                                       |

|-----------------|-----------------------------------------------|

| Horer's Rule    | $5 \cdot (T_{mul} + T_{add})$                 |

| Dorn's Method   | $T_{sq} + 3 \cdot T_{mul} + 3 \cdot T_{add}$  |

| Estrin's Method | $2 \cdot T_{sq} + T_{mul} + T_{add}$          |

| Proposed Method | $2 \cdot T_{sqr} + T_{mul} + 3 \cdot T_{add}$ |

Table 5.1: Latency for evaluating  $5^{th}$  degree polynomials using proposed method vs. conventional methods.

| Method          | Multiplier | Squarer | Adder |

|-----------------|------------|---------|-------|

| Horner's Rule   | 5          |         | 5     |

| Dorn's Method   | 6          | 1       | 5     |

| Estrin's Method | 5          | 2       | 5     |

| Proposed Method | 3          | 3       | 5     |

Table 5.2: Hardware macro count for evaluating  $5^{th}$  degree polynomials using proposed method vs. conventional methods.

squarer exists (i.e. where a squarer circuit is more efficient than a general multiplier). The proposed method shows a tremendous advantage over the other two parallel methods, where the expense of parallelism is very much higher.

As mentioned, the advantage over Horner's rule presupposes the existence of an efficient squarer. If the design published in [51] is used, the requirement is met without doubt. In fact, a novel efficient squarer (on reconfigurable hardware) has been invented during the course of this research, which will be discussed in the Chapter 6. The combined benefit of the novel polynomial evaluation process using the novel squarer will be shown in the system implementation results for the overall polynomial evaluation process, presented later.

#### 5.3 Generalized Format

The novel polynomial method presented here can, of course, be generalized to higher degree. The process of generalization will now be explained in detail. Consider a general  $k^{th}$  degree polynomial in (Eq. 1.1), Define an integer number j, which is the binary

logarithm of k:

$$j = \lceil log_2 k \rceil \tag{Eq. 5.6}$$

Then the equation can be divided into the following groups,

$$f(x) = (a_k x^k + a_{k-j} x^{k-j} + a_{k-2j} x^{k-2j})$$

$$+ (a_{k-1} x^{k-1} + a_{k-j-1} x^{k-j-1} + a_{k-2j-1} x^{k-2j-1}) + \dots$$

$$+ (a_{k-j+1} x^{k-j+1} + a_{k-2j+1} x^{k-2j+1} + a_{k-3j+1} x^{k-3j+1})$$

(Eq. 5.7)

If k-3j+1>0, i.e. the polynomial is greater than  $20^{th}$  degree, more elements shall be grouped after the above equation using the same general principle. Here, for reasons of space and the scope of the thesis, only examples for degree less than 20 are presented. Let us now define,

$$p_t(x) = (a_{k-t}x^{k-t} + a_{k-j-t}x^{k-j-t} + a_{k-2j-t}x^{k-2j-t})$$

(Eq. 5.8)

Where, t ranges from [0, j-1]. In  $p_t(x)$ , a common divisor of  $a_{k-t}x^{k-2j-t}$  must be extracted so that the equation becomes,

$$p_t(x) = a_{k-t}x^{k-2j-t}\left(x^{2j} + \frac{a_{k-j-t}}{a_{k-t}}x^j + \frac{a_{k-2j-t}}{a_{k-t}}\right)$$

(Eq. 5.9)

Applying the method proposed in Hypothesis 1 and then (Eq. 5.9) becomes,

$$p_t(x) = a_{k-t}x^{k-2j-t}(x^j + m_{k-t}^2) + n_{k-t}$$

(Eq. 5.10)

and

$$f(x) = p_0 + p_1 + \dots + p_{i-1}$$

(Eq. 5.11)

Equation (Eq. 5.10) and (Eq. 5.11) are the general format for the proposed method to evaluate polynomials with arbitary degree.

#### Derivation of the Coefficient Set and Accuracy 5.4 Concern

The proposed method needs a new set of coefficients, which are a one-off derivation from the original coefficients. For example, in (Eq. 5.4) the new set of coefficients would be computed from the following,

$$m_5 = \frac{a_3}{2a_5}$$

(Eq. 5.12)

$$m_5 = \frac{a_3}{2a_5}$$

(Eq. 5.12)

$m_4 = \frac{a_2}{2a_4}$  (Eq. 5.13)

$$n_5 = \frac{a_1}{a_5} - \frac{a_3^2}{4a_5^2} \tag{Eq. 5.14}$$

$$n_4 = \frac{a_0}{a_4} - \frac{a_2^2}{4a_4^2} \tag{Eq. 5.15}$$

For an application such as an adaptive filter, this may result in an additional overhead every time the polynomial adapts, however the evaluation process can be performed when deriving the polynomial. Even when the coefficients are computed on the fly, compared to the approximation process, this overhead is small and tends to zero as the number of evaluations performed using the new coefficient set becomes large. In the system considered in this thesis, the coefficients are all pre-stored in RAM when developing the RTL and this overhead will not need to be accounted for. In fact, this is considered to be a typical real-world scenario – where the polynomial is generated during system setup or programming, rather than on the fly.

In such real systems, especially when fixed point format processing is used for computation, the new set of coefficients might result in a larger evaluation error than if the original set was used. This important consideration will be discussed as part of the system implementation discussions, where guard bits may be needed to maintain the accuracy.

One has to note that in certain conditions, when  $n_5$  and  $n_4$  requires large wordlength to keep precisions on both  $a_1$  and  $a_0$ , extremely large multiplications might be incurred. This is not desired as it will penalize the performance gain. An alternative equation could be used instead of (Eq. 5.4) and the new format is shown in (Eq. 5.16).

$$f(x) = [a_5 \cdot (x^2 + m_5')^2 + n_5'] \cdot x + a_4(x^2 + m_4')^2 + n_4'$$

(Eq. 5.16)

where,

$$m_5' = \frac{a_3}{2a_5} \tag{Eq. 5.17}$$

$$m_4' = \frac{a_2}{2a_4} \tag{Eq. 5.18}$$

$$n_5' = a_1 - \frac{a_3^2}{4a_5} \tag{Eq. 5.19}$$

$$n_4' = a_0 - \frac{a_2^2}{4a_4} \tag{Eq. 5.20}$$

The alternative equation has the same hardware cost compared to hypothesis 2 shown in Table 5.3. The penalty is one more multiplication stage inserted in the critical path for polynomial whose degree is higher than 4 (but only one even when degree goes up). This will increase the latency for polynomial evaluators, however, it may not be significant in real-world and it will be discussed in the later chapters.

The alternative equation is used in Chapter 7 to account for the problem in the real application. It will compare the latency between novel method and Estrin's method in both  $4^{th}$  and  $5^{th}$  degree polynomial, where the later one has slightly longer latency in the novel method compared to Estrin's method.

| Method               | Multiplier | Squarer | Adder |

|----------------------|------------|---------|-------|

| Alternative Equation | 3          | 3       | 5     |

| Proposed Method      | 3          | 3       | 5     |

Table 5.3: Hardware macro count for evaluating  $5^{th}$  degree polynomials using alternative equation vs. proposed methods.

## 5.5 Motivation of Squarer and Reconfigurable Hardware Implementation

implemention the novel method in reconfigurable hardware, specifically FPGAs, rather than ASIC has been completed. It is not cost effective to build a polynomial evaluation unit in ASIC for each individual application, where different applications need to be optimized based on different precision, area and performance requirements. However, it is convenient to build the design in FPGA, where data paths are highly customizable and the development duration and financial cost are acceptable at the same time. In the modern FPGAs, where more dedicated functional blocks such as DSPs and BRAMs are available, it becomes much more efficient to map such application specific processing units onto FPGA.

The efficiency of the novel method largely depends on how well the squarer is designed. Conventional squarers mainly rely on the benefits of folding the partial products, compared to the situation in the parallel multiplier. When targeting to implement the system on FPGA, exploration of various squarer structures has been done and it has been decided to build an efficient squarer based on modern FPGA architecture, proposed in the subsequent chapter.

## Chapter 6

# Novel Squarer Implementation on FPGA

### 6.1 Proposed Design

In this chapter we propose an optimised squaring algorithm implementation on FPGA with lower DSP block cost. The algorithm is flexible with respect to operand size, though it targets higher wordlength, since (as will be shown later) it improves on existing methods when operand sizes are equal or larger than 42 bits.

The algorithm was inspired by the same Karatsuba-Ofman algorithm. However, the same reduction in [36] does not apply for squaring. According to equations in [56], there are no more advantages in using the reformation if both inputs are the same. We have thus modified the classic Karatsuba-Ofman algorithm, only applying specific parts of the process. By rearranging the squaring equation using our proposed algorithm, functions performed by the DSP blocks can be mapped to a small number of LUTs. As wordlength increases, more DSPs can be exchanged with LUTs, and the LUT count grows only gradually. We demonstrate the algorithm using two cases in the following.

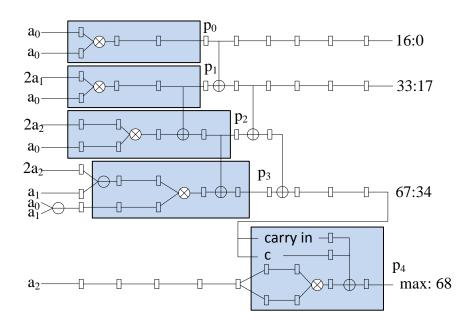

### 6.1.1 Squarers for Three Splits Input

We will take a  $52\times52$  bit squarer to illustrate the algorithm, where equation (Eq. 4.2) was the equivalent squaring equation using the cascaded method. We now define m and

n as,

$$m = a_2 - a_1$$

(Eq. 6.1)

$$n = 2a_0 - a_1 (Eq. 6.2)$$

and their product as,

$$m \cdot n = 2a_2a_0 - 2a_1a_0 - a_2a_1 + a_1^2$$

(Eq. 6.3)

This can be rewritten to provide the term  $a_1^2 + 2a_2a_0$  (which was in the middle of (Eq. 4.2)) as,

$$a_1^2 + 2a_2a_0 = mn + 2a_1a_0 + a_2a_1$$

(Eq. 6.4)

Now substituting (Eq. 6.4) into (Eq. 4.2) gives the following,

$$x \cdot x = a_0^2$$

$$+ 2a_1 a_0 \cdot 2^{17}$$

$$+ (mn + 2a_1 a_0 + a_2 a_1) \cdot 2^{34}$$

$$+ 2a_2 a_1 \cdot 2^{51}$$

$$+ a_2^2 \cdot 2^{68}$$

(Eq. 6.5)

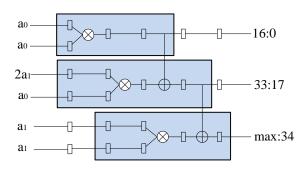

In the formulation of (Eq. 6.5), we can see that only 5 DSP blocks are required. The DSPs are configured to compute the sub products  $a_0^2$ ,  $2a_1a_0$ ,  $a_2a_1$ , mn and  $a_2^2$  (named DSPs  $p_0$   $p_1$   $p_2$   $p_3$  and  $p_4$ ). The repeated terms will be added using LUTs or post-adders in the DSP blocks. Compared to the 6 DSP blocks needed in the cascaded method, one fewer DSP block is required (16.7% saving), matching the DSP block savings of the tiling method (also note that DSP reduction becomes greater as the operand word size increases).

The main benefit of this transformation is the reduced cost for the replacement logic: The overhead in the algorithm is two 17 bit adders needed to compute m and n, and adders to accumulate those sub products that cannot be added using the post-adders in the DSP blocks. Compared to the tiling method, which requires small multiplies and complex additions, a careful mapping of the adders in our algorithm can significantly reduce the extra LUT overhead. Specifically, for Virtex 6 FPGAs, it only requires one 17 bit adder using LUTs to work out one of m or n, since the other can be computed using the pre-adder in DSP block  $p_3$ . On the other hand, the remaining addition has to be mapped efficiently with two cascaded chains which can be found from (Eq. 6.5). The two chains are,

$$chain_0 = 2a_1a_0 + a_2a_1 \cdot 2^{17} + mn \cdot 2^{17}$$

(Eq. 6.6)

$$chain_1 = 2a_1a_0 + 2a_2a_1 \cdot 2^{17}$$

(Eq. 6.7)

$chain_0$  is the output directly from DSPs  $p_3, p_2$  and  $p_1$  with the cascaded addition chain.  $chain_1$  can be computed in the form of

$$2a_1a_0 + a_2a_1 \cdot 2^{17} + a_2a_1 \cdot 2^{17}$$

(Eq. 6.8)

which can be easily derived from  $p_2$  and  $p_1$  in LUTs as well. During the same cycle of finishing  $chain_0$ , the second chain finishes the addition so that they are summed up in the following cycle. The whole process requires one 34-bit adder to obtain  $chain_1$  and one 51-bit adder to add the two chains. Figure 6.1 shows the overall implementation schematic of this squaring circuit with pipeline registers.