# Optimization and Scheduling of Applications in a Heterogeneous CPU-GPU Environment

Submitted to the School of Computer Engineering of Nanyang Technological University for fullfillment of the Degree of Master of Engineering

by

Karan Rajendra Shetti G1003232J

under the guidance of

Asst. Prof. Suhaib A. Fahmy

School of Computer Engineering

Jan 2014

#### Abstract

With the emergence of General Purpose computation on GPU (GPGPU) and corresponding programming frameworks (OpenCL, CUDA), more applications are being ported to use GPUs as a co-processor to achieve performance that could not be accomplished using just the traditional processors. However, programming the GPUs is not a trivial task and depends on the experience and knowledge of the individual programmer. The main problem is identifying which task or job should be allocated to a particular device. The problem is further complicated due to the dissimilar computational power of the CPU and the GPU. Therefore, there is a genuine need to optimize the workload balance.

This thesis presents the work done toward the author's post graduate study and describes the optimization of the Heterogeneous Earliest Finish Time (HEFT) algorithm in the CPU-GPU heterogeneous environment.

In the initial chapters, different scheduling principles available are described and an in depth analysis of three state of the art algorithms for the chosen heterogeneous environment is presented. A comparison of fine-grained with coarse-grained scheduling paradigms is also studied. Using state of the art StarPU scheduling framework and exhaustive benchmarks, it is shown that the fine grained approach in much more efficient for the CPU-GPU environment.

A novel optimization of the HEFT algorithm that takes advantage of dissimilar execution times of the processors is proposed. By balancing the locally optimal result with the globally optimal result, it is shown that performance can be improved significantly without any change in the complexity of the algorithm (as compared to HEFT). HEFT-NC (No-Cross) is compared with HEFT both in terms of speedup and schedule length. It is shown that the HEFT-NC outperforms HEFT algorithm and is consistent across different graph shapes and task sizes.

### Acknowledgements

I would firstly likely to thank Dr. Suhaib Fahmy for giving me the opportunity to complete my Master's program. I would like to especially thank him for his patience and understanding while I was trying to juggle a job, coursework and the thesis.

I would also like to thank my supervisor at Airbus Innovations, Singapore, Dr Timo Bretschneider, without whose support and encouragement, this endeavor would have been very difficult. His constant support and push to improve my work has helped tremendously and also his role as the devil's advocate has improved the overall quality of my work. I would also like to thank my colleague Asha for being my sounding board and encouraging me to continue working by sharing her experiences of her PhD.

I would also like to thank my family for their unflinching support and belief in me, and my housemates, Shantanu, Danny, Aiyappa and Khurana for their support and encouragement. I truly appreciate the patience they have shown me and also respecting my need for a peaceful environment at home. Finally I would like to thank my girlfriend Satvika, who in more ways than one made sure I completed this program. Her encouragement and support has never wavered and she has helped me strive harder to complete this study.

Karan R Shetti Jan 2014 Nanyang Technological University, Singapore

# Contents

| 1        | Intr                 | oducti  | ion                                              | 3  |

|----------|----------------------|---------|--------------------------------------------------|----|

|          | 1.1                  | Proble  | em Statement                                     | 5  |

|          |                      | 1.1.1   | Constraints                                      | 6  |

|          | 1.2                  | Key C   | Contributions                                    | 6  |

|          | 1.3                  | Organ   | nization of the Report                           | 6  |

| <b>2</b> | Lite                 | erature | e Review                                         | 9  |

|          | 2.1                  | Sched   | uling algorithms in homogeneous architectures    | 9  |

|          |                      | 2.1.1   | Partitioned Scheduling algorithms                | 10 |

|          |                      | 2.1.2   | Global scheduling algorithms                     | 10 |

|          |                      | 2.1.3   | Heuristic based scheduling algorithms            | 11 |

|          | 2.2                  | Advar   | nces in Heterogeneous architectures              | 14 |

|          |                      | 2.2.1   | Heterogeneous architectures                      | 14 |

|          | 2.3                  | Sched   | uling algorithms in heterogeneous architectures  | 16 |

|          | 2.4                  | Curre   | nt models and frameworks for CPU-GPU environment | 18 |

|          |                      | 2.4.1   | Harmony Model                                    | 18 |

|          |                      | 2.4.2   | Predictive runtime scheduling                    | 19 |

|          |                      | 2.4.3   | Static Partitioning using OpenCL                 | 20 |

|          | 2.5                  | Summ    | nary                                             | 22 |

| 3        | $\operatorname{Pro}$ | gramn   | ning Framework                                   | 23 |

|          | 3.1                  | Introd  | luction                                          | 23 |

|          | 3.2                  | Open(   | CL Application Programming Interface             | 24 |

|          |                      | 3.2.1   | Platform Model                                   | 24 |

|          |                      | 3.2.2   | Execution Model                                  | 24 |

|          |                      | 3.2.3   | Memory Model                                     | 27 |

|          |                      | 3.2.4   | Summary                                          | 27 |

|          | 3.3                  | StarP   | U Scheduling Interface                           | 28 |

|          |                      | 3.3.1   | Programming Interface [1]                        | 29 |

|          |                      | 3.3.2   | Task Scheduling [1]                              | 30 |

|          |                      | 3.3.3   | Summary                                          | 33 |

iv

| 4 | Fine | e Grain  | ned Scheduling                   | 35   |

|---|------|----------|----------------------------------|------|

|   | 4.1  | Introdu  | action                           | . 35 |

|   | 4.2  | Multi-s  | step Applications                | . 36 |

|   |      | 4.2.1    | Example 1                        | . 36 |

|   |      | 4.2.2    | Example 2                        | . 36 |

|   |      | 4.2.3    | Example 3                        | . 38 |

|   | 4.3  | Experi   | ments and Discussion             | . 39 |

|   | 4.4  | Results  | s and Discussion                 | . 40 |

|   |      | 4.4.1    | 256 Matrix dataset               | . 40 |

|   |      | 4.4.2    | 1024 Matrix dataset              | . 43 |

|   |      | 4.4.3    | 512 Matrix dataset               | . 46 |

|   |      | 4.4.4    | Device Utilization               | . 49 |

|   | 4.5  | Summa    | ary and Conclusion               | . 51 |

| 5 | HE   | FT-No    | Cross Algorithm                  | 53   |

|   | 5.1  | Introdu  | uction                           | . 53 |

|   | 5.2  | Probler  | m Statement                      | . 54 |

|   | 5.3  | Algorit  | chm Overview                     | . 55 |

|   |      | 5.3.1    | Modification of Task Weight      | . 55 |

|   |      | 5.3.2    | No-Crossover Scheduling          | . 58 |

|   | 5.4  | Results  | s and Discussion                 | . 61 |

|   |      | 5.4.1    | Experimental Setup               | . 61 |

|   |      | 5.4.2    | Simulation Results               | . 61 |

|   | 5.5  | Conclu   | sion                             | . 65 |

|   |      | 5.5.1    | Future Work                      | . 65 |

| 6 | Ext  | ension   | of the HEFT-NC Algorithm         | 67   |

|   | 6.1  | Introdu  | uction                           | . 67 |

|   | 6.2  | Algorit  | chm Overview                     | . 68 |

|   |      | 6.2.1    | Modification of Task Weight      | . 68 |

|   |      | 6.2.2    | No-Crossover Scheduling          | . 68 |

|   | 6.3  | Results  | s and Discussion                 | . 70 |

|   |      | 6.3.1    | Experimental Setup               | . 70 |

|   |      | 6.3.2    | Simulation Results               | . 70 |

|   | 6.4  | Conclu   | sion                             | . 74 |

| 7 | Cor  | nclusion | and Future Work                  | 75   |

|   | 7.1  | Conclu   | sion                             | . 75 |

|   | 7.2  | Future   | Work                             | . 77 |

|   |      | 7.2.1    | Extensions to proposed algorithm | . 77 |

|   |      | 7.2.2    | Real world platform testing      | . 78 |

| CONTENTS | v |

|----------|---|

|          |   |

| 79 |

|----|

| 79 |

| 79 |

| 79 |

| 80 |

|    |

vi CONTENTS

# List of Figures

| 1.1  | Simplistic model of HSA                            | 4  |

|------|----------------------------------------------------|----|

| 1.2  | Kaveri: Internal architecture                      | 5  |

| 3.1  | OpenCL platform model [2]                          | 25 |

| 3.2  | Work-item/Work-group example [2]                   | 25 |

| 3.3  | OpenCL memory model [2]                            | 27 |

| 3.4  | Complete OpenCL framework [2]                      | 28 |

| 3.5  | Performance model of Matrix Multiplication         | 29 |

| 3.6  | Execution timeline of multiple tasks               | 31 |

| 3.7  | Execution model of StarPU [1]                      | 33 |

| 4.1  | Performance model for recursive Gaussian task      | 37 |

| 4.2  | Performance model for <i>matrix transpose</i> task | 37 |

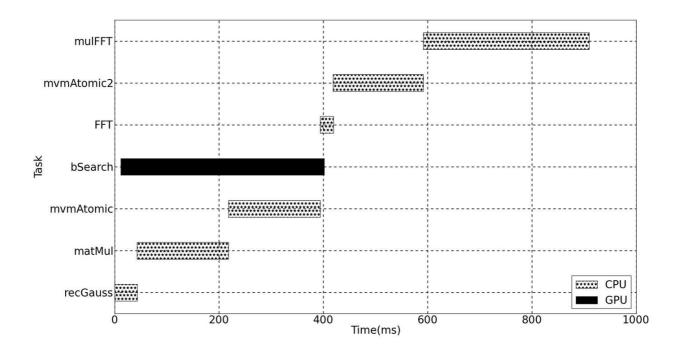

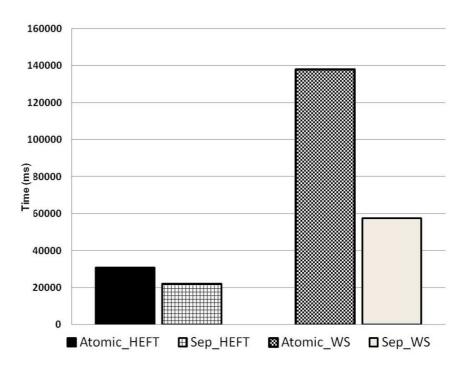

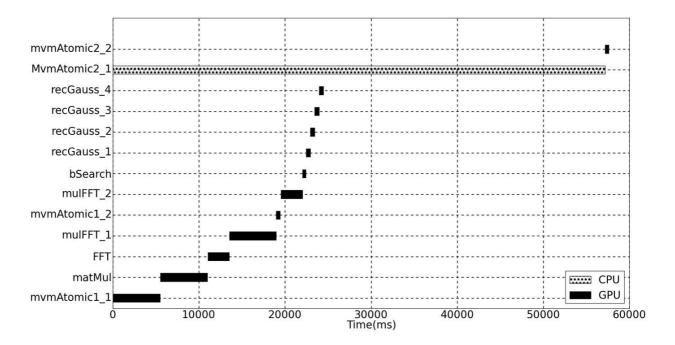

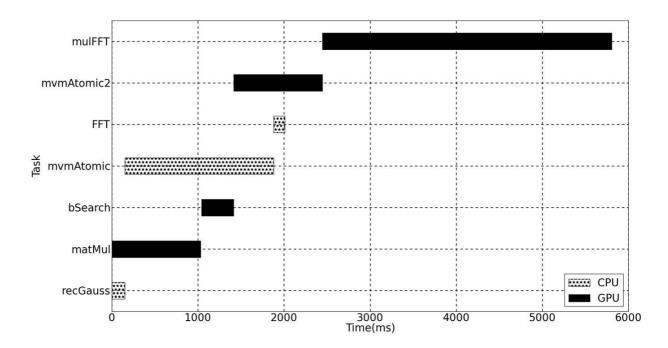

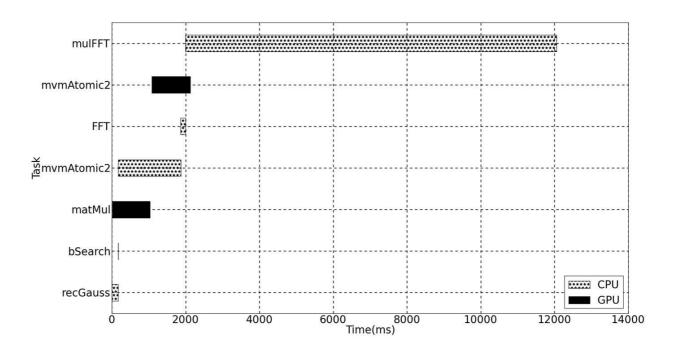

| 4.3  | Execution Time - 256 dataset                       | 40 |

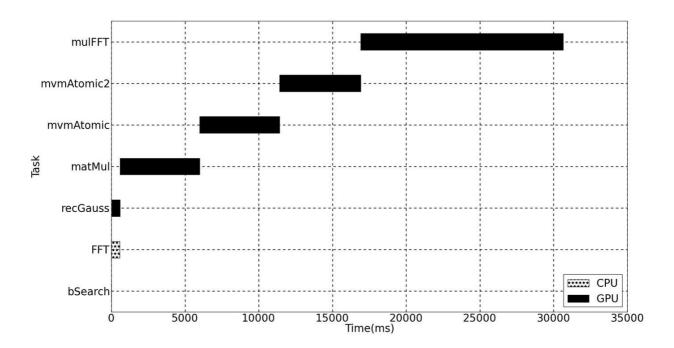

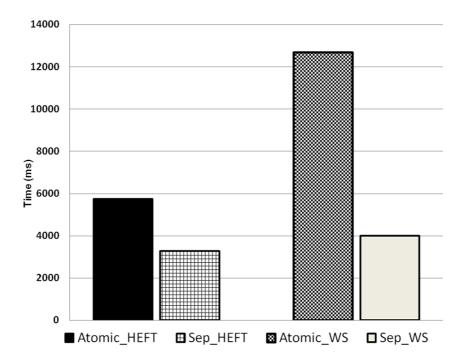

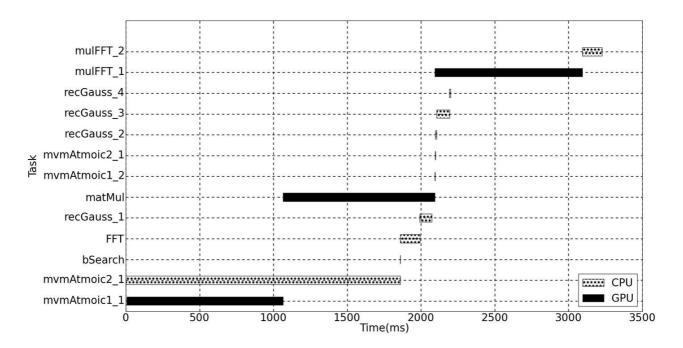

| 4.4  | Atomic HEFT - 256 Dataset                          | 41 |

| 4.5  | Atomic WS - 256 Dataset                            | 41 |

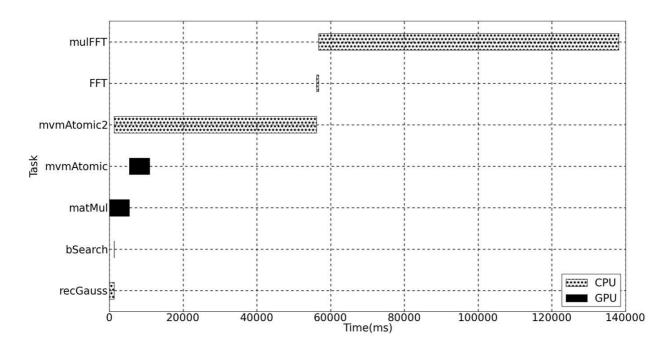

| 4.6  | Non Atomic HEFT - 256 Dataset                      | 42 |

| 4.7  | Non Atomic WS - 256 Dataset                        | 42 |

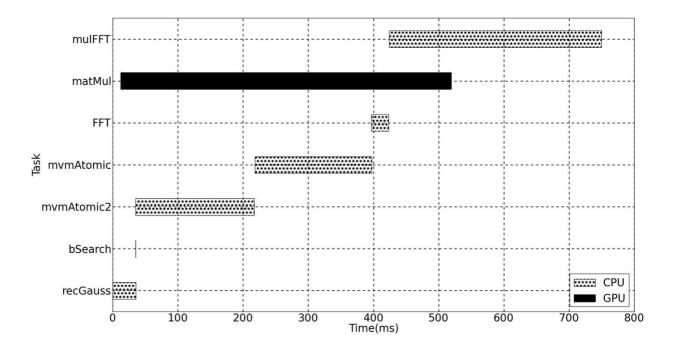

| 4.8  | Execution Time - 1024 dataset                      | 43 |

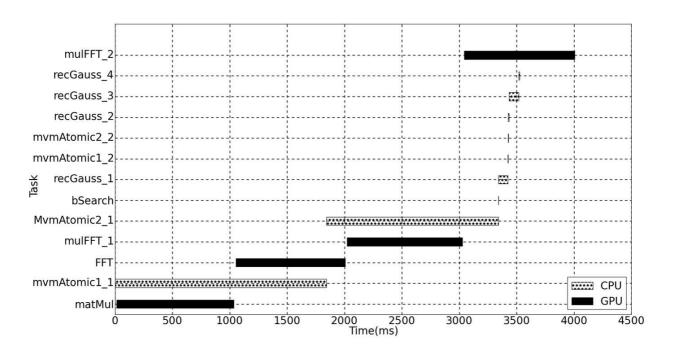

| 4.9  | Atomic HEFT - 1024 dataset                         | 44 |

| 4.10 | Atomic WS - 1024 dataset                           | 44 |

| 4.11 | Non-Atomic HEFT - 1024 dataset                     | 45 |

| 4.12 | Non-Atomic WS - 1024 dataset                       | 45 |

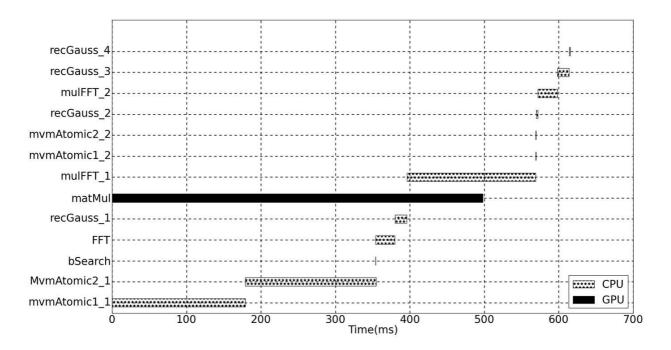

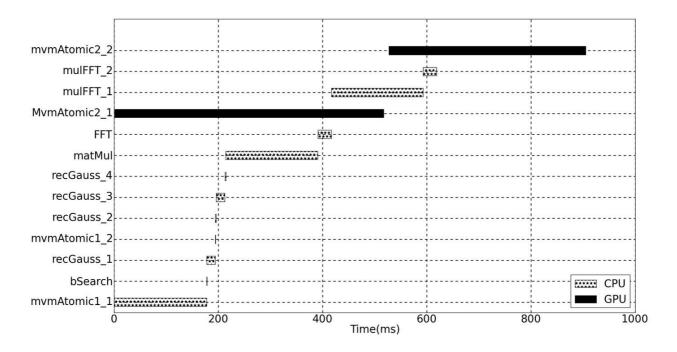

| 4.13 | Execution Time - 512 dataset                       | 46 |

| 4.14 | Atomic HEFT - 512 Dataset                          | 47 |

| 4.15 | Atomic WS - 512 Dataset                            | 47 |

| 4.16 | Non-Atomic HEFT - 512 dataset                      | 48 |

| 4.17 | Non-Atomic WS - 512 dataset                        | 48 |

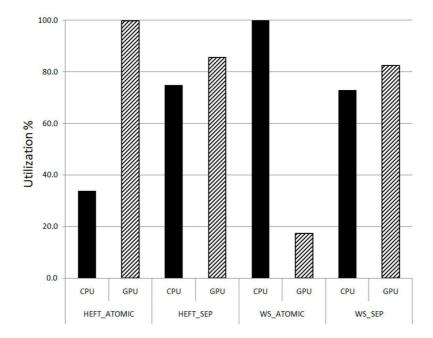

| 4.18 | Utilization of CPU and GPU                         | 50 |

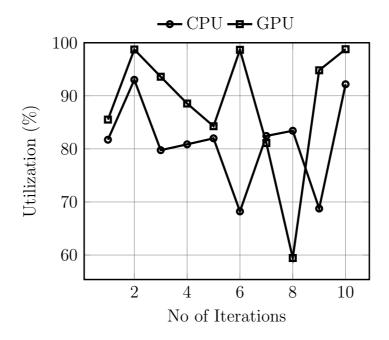

| 4.19 | Utilization of devices - Work Steal                | 50 |

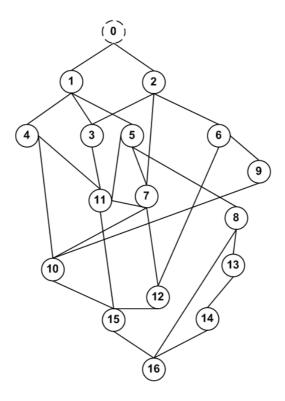

| 5.1  | Example of random DAG                              | 57 |

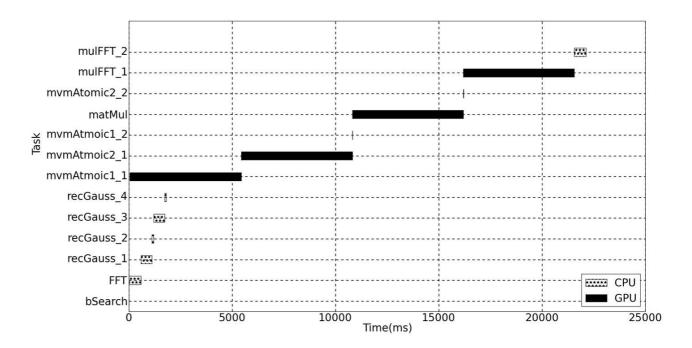

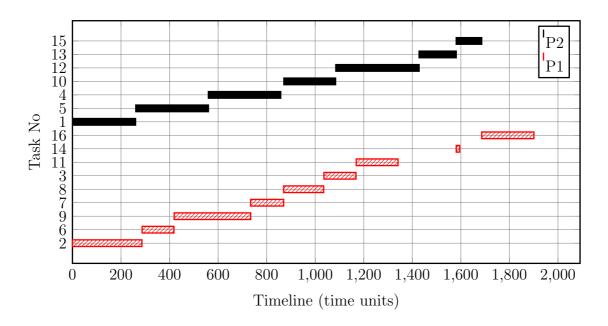

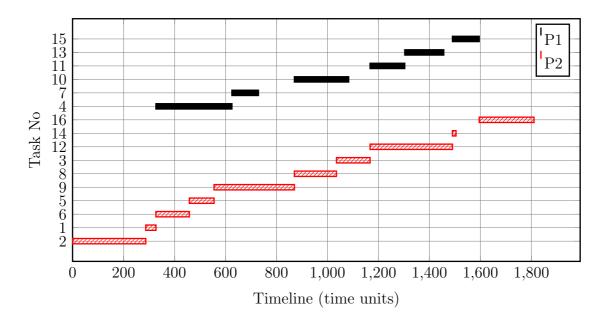

| 5.2 | Application trace of HEFT                                           | 60 |

|-----|---------------------------------------------------------------------|----|

| 5.3 | Application trace of HEFT-NC                                        | 60 |

| 5.4 | Speedup comparison $\alpha = 0.1 \dots \dots \dots \dots \dots$     | 62 |

| 5.5 | Speedup comparison $\alpha = 5 \dots \dots \dots \dots \dots \dots$ | 62 |

| 5.6 | Speedup comparison $\alpha = 10 \ldots \ldots \ldots \ldots \ldots$ | 63 |

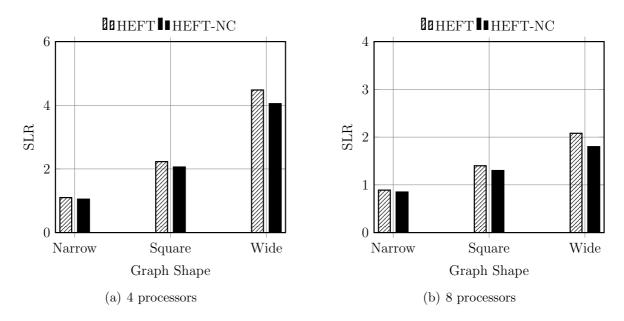

| 5.7 | SLR comparison over different graph shapes                          | 63 |

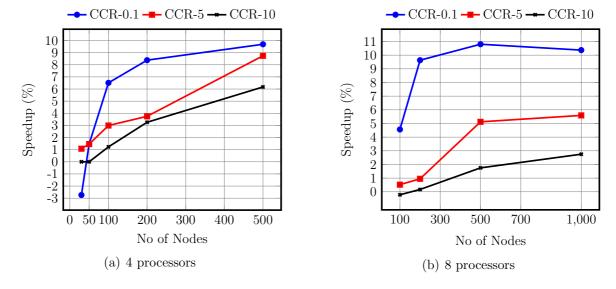

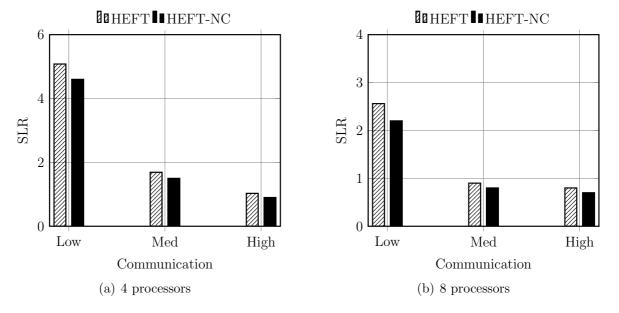

| 5.8 | SLR comparison over different CCR                                   | 64 |

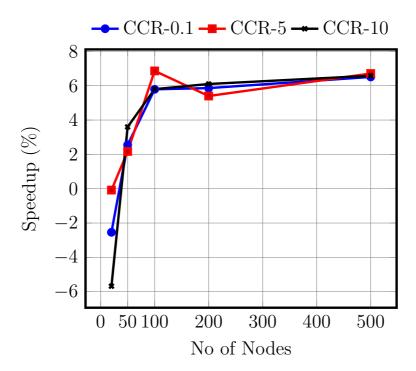

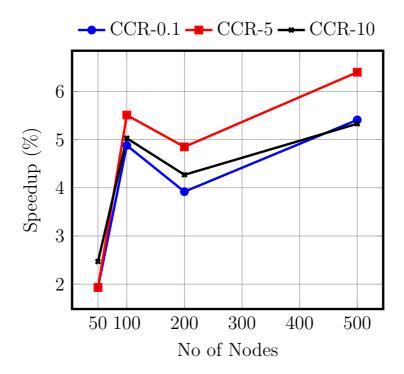

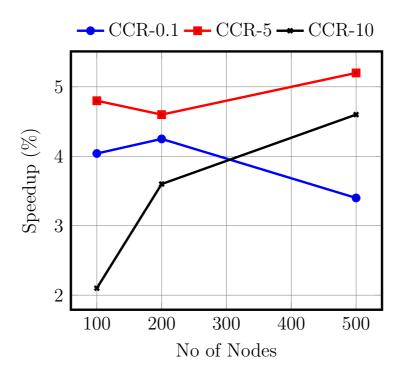

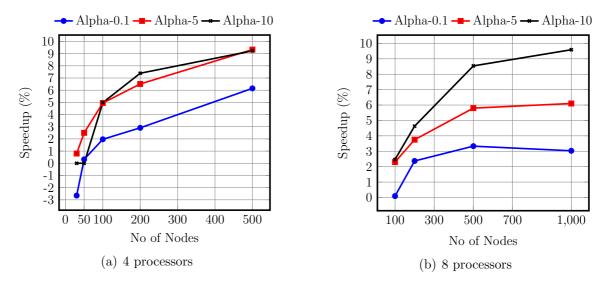

| 6.1 | Speedup comparison across different CCR, for given shape (alpha)    | 71 |

| 6.2 | Speedup comparison across different alpha, for given CCR            | 71 |

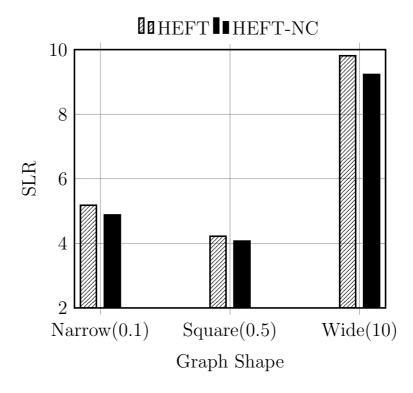

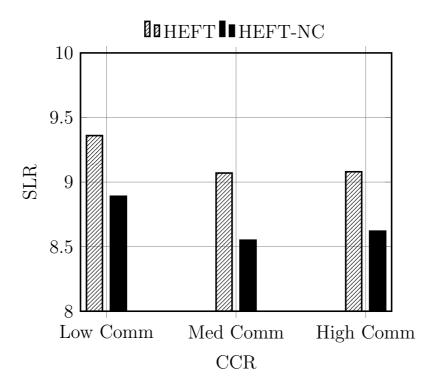

| 6.3 | SLR comparison over different graph shapes                          | 73 |

| 6.4 | SLR comparison over different communication ratios                  | 73 |

# List of Tables

| 4.1 | Execution time for mvmAtomic Task (in ms) | 36 |

|-----|-------------------------------------------|----|

| 4.2 | Execution time for mulFFT Task (in ms)    | 38 |

| 5.1 | DAG Rank table                            | 57 |

| 5.2 | Definitions                               | 59 |

| 5.3 | SLR comparison over varying CCR           | 64 |

| 6.1 | Definitions                               | 69 |

| 6.2 | Average SLR for 4 processors              | 72 |

| 6.3 | Average SLR for 8 processors              | 72 |

| A.1 | CPU specification                         | 79 |

| A.2 | CPU specification                         | 79 |

# Chapter 1

# Introduction

The computing requirements of applications have been growing at a rapid pace. Conventional single core processors are incapable of delivering the required processing power as they are unable to overcome the three walls: Memory, Instruction level parallelism and Power wall. Even the traditional method of increasing performance, i.e. increasing clock frequency is not always optimal and after a point physically infeasible [3]. Multi-core CPU and many-core GPU (Graphical Processing Unit) have been able to alleviate this problem and have emerged as a cost effective means of scaling applications [3]. The modern GPU is a specialized hardware, which is able to execute highly parallel computations. It focuses more on data processing rather than caching and flow control [4]. GPUs which have traditionally been used for graphic rendering are now increasingly being used for non-graphical applications. This has given birth to a new field of study called GPGPU (General Purpose computation on GPU) [5] and owing to its high performance, GPUs are increasingly being used in image processing, simulations, spectral analysis and other scientific applications [6]. Keeping in mind these processing capabilities of GPU, significant research has been conducted to seek ways to use the power of GPUs for general purpose computing [7, 8, 9, 10, 11]. However, programmability of GPU still remains a challenging task. It has become easier with the introduction of programming frameworks like OpenGL, CUDA and OpenCL. However, all these frameworks require manual memory management and work distribution, which makes it more challenging as sub optimal programming can severely degrade performance [8]. While GPUs have impressive computing power, their specialized hardware may not be optimal for some applications, i.e. algorithms need to be inherently parallel and involve enough data processing to overcome memory latencies. This has led to the trend of using both CPU and GPU in a heterogeneous environment. This technique has been successful as most desktops and notebooks are equipped with multi-core CPU and GPU. AMD has recently introduced new fusion processors called APU (Accelerated Processing Units) which combine both CPU and GPU in one chip [7, 12]. In the case of the APU, the CPU and GPU work in tandem with shared system memory, and the key advantage here is lower power consumption when

4 Introduction

running modern applications that are designed to leverage on the advantages of both the CPU and GPU. Applications that deal with analytics, search and facial recognition are some aspects that stand to gain from this boost [13].

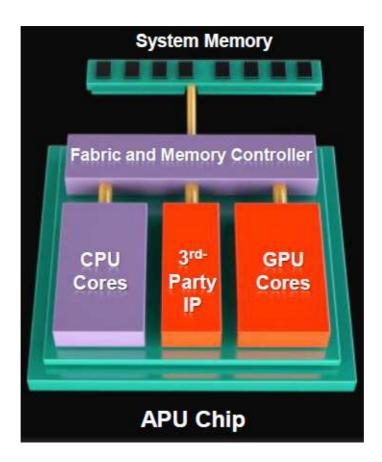

Continuing the APU model, AMD has also launched a new genre of chips following the Heterogeneous System Architecture standard [13]. HSA is essentially an enabler that allows multiple processing units (or accelerators) to work in tandem with shared system resources. A simplistic diagram of the HSA architecture is shown in Fig. 1.1

Figure 1.1: Simplistic model of HSA

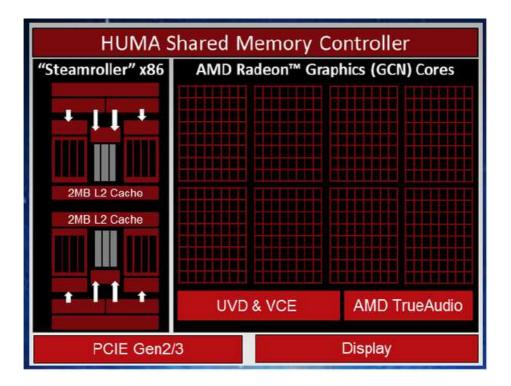

An example of this second generation APUs is the Kaveri chip launched by AMD [14]. As shown in figure 1.2, Kaveri is capable of having four multi-threaded "Steamroller" CPU cores with a 3.7 GHz clock and 512 Radeon Series GPU cores with a 720 MHz core frequency.

Similarly, Intel has introduced the Sandy Bridge and Ivy Bridge processors like the Haswell range of microprocessors. The focus here is to provide better performance and graphics for mobile platforms while reducing the power consumed. These examples clearly show the continued industrial interest in such a trend.

The GPU is hence seen more as co-processor to a CPU and the focus has now shifted to exploiting the power of both CPU and GPU in solving generic problems. In order to improve application performance and explore heterogeneity, methods to distribute or schedule work across these asymmetric PUs (Processing Units) have become

Figure 1.2: Kaveri: Internal architecture

more important. Conventional scheduling algorithms may not be optimal due to dissimilar execution times and possibly different communication rates. The main goal of any scheduling algorithm is to assign a task to the best suited processor such that the overall execution time (make-span) is minimized. This problem of assigning tasks to the most efficient processor is known to be NP-hard [15] and hence most scheduling algorithms are based on heuristics.

### 1.1 Problem Statement

A platform is considered heterogeneous when dissimilar computing architectures are coupled together to increase the overall computing power and solve problems faster. The introduction of new heterogeneous architecture has led to an immense improvement in performance at a lower cost, but also has given rise to many challenges, as the rate of execution of tasks is different on each processor.

This property of dissimilar execution time in heterogeneous environments has reinvigorated research in task scheduling. Applications like image-filtering, face recognition, gesture recognition and audio processing are multi-step processes. There are cases when certain steps within such applications may have skewed performance on a single device. In problems involving multi-step applications, it is crucial to determine which sections are more efficient on a particular device.

Keeping in mind the above points, the author intends to study the problem of mapping a set of N tasks, to a heterogeneous environment represented by a CPU and GPU such that

6 Introduction

the overall execution time of the application is minimized. As this problem has a non polynomial solution, an approximate heuristic solution will be investigated. It is intended to simplify this process by using predetermined information derived from static profiling (automatic or manual).

### 1.1.1 Constraints

- The problem of finding a mapping for a set of tasks N to set of processing elements is an NP hard problem. This implies only heuristic solutions can be found.

- The proposed schedule can only be non-preemptive as GPUs do not support preemption.

- In order to reduce the complexity of framework, an application level as compared to a driver level approach is used.

# 1.2 Key Contributions

Some of the key contributions of this thesis are:

- 1. A broad survey and analysis of the current literature on task scheduling in both homogeneous and heterogeneous environments is presented. An in-depth analysis of the more relevant literature is then discussed.

- 2. Using the state of the art StarPU framework, a comparison study between fine-grained and coarse grained scheduling for the chosen environment was undertaken. Several benchmarks were used and results are analyzed over different data sizes.

- 3. A novel optimization to the Heterogeneous Earliest Finish Time(HEFT) algorithm for the CPU-GPU environment is presented. The author is able to demonstrate significant improvements in its performance without changing the complexity of the algorithm.

## 1.3 Organization of the Report

This report is organized as follows. Chapter 2 provides a comprehensive review of relevant strategies used to schedule tasks both in the homogeneous and heterogeneous environments. It also provides a critique of the strategies that can be used for a CPU-GPU environment. Chapter 3 provides a broad overview and justification of the different programming frameworks used in this thesis. Chapter 4 presents the results of comparison between a fine-grained approach and coarse-grained approach to scheduling tasks in a CPU-GPU environment. Based on the results derived from chapter 4, chapters 5

6 put forward the different optimizations to the HEFT algorithm. Finally, Chapter 7 summarizes the work presented and suggest future work in the area

8 Introduction

# Chapter 2

# Literature Review

Parallel computing is a form of computation in which multiple operations are carried out simultaneously [16]. It has evolved from the principle, that large problems can often be divided into smaller ones, which are then solved in parallel [16]. Depending on the type of hardware architecture, parallel computers can be broadly classified into homogeneous and heterogeneous platforms [17]. Homogeneous include platforms such as multi-core, many-core, grid computing and clusters. Here the processors are similar, so all tasks execute with the same rate. A platform is considered heterogeneous when dissimilar computing architectures are coupled together, for accelerating specific tasks. Therefore, In some cases, the rate of execution of tasks is different on each processor and in some, tasks may not be able to run on all processors. The introduction of these new heterogeneous architectures has led to immense improvements in performance at lower cost, but they have also given rise to many challenges. One of the interesting areas of research has been the scheduling of tasks or programs between the specialized hardware and the traditional processor. In Section 2.1, a brief introduction of the scheduling algorithms available for homogeneous architectures is presented. This section describes the different scheduling paradigms and provides insight for development in a heterogeneous environment. In section 2.2, the advances and strategies used for high performance computing, particularly in heterogeneous environments is presented. The latest advances in task scheduling algorithms in CPU-GPU heterogeneous environment is elaborated in Section 2.3. Finally in Section 2.4, a detailed account of some of the current models and frameworks for task scheduling in CPU-GPU environment are presented

# 2.1 Scheduling algorithms in homogeneous architectures

An application (or task set) is assumed to comprise a static set of n tasks. These tasks give rise to a potentially infinite sequence of invocations (or jobs) [17]. Therefore task scheduling in multi processor architecture is basically trying to solve two problems, i.e.

Allocation problems and Priority problems. Within the domain of allocation problems, the level of task migration is used to classify different scheduling algorithms [17]

- No Migration: Migration of tasks and jobs is not allowed as each task is allocated to a processor.

- Task-level migration: Jobs of one task can execute on different processors, however each processor can execute only one job.

- Job-level migration: A single job is allowed to migrate and execute on different processors. This level migration gives the highest level of freedom. The only restriction is that parallel execution of a single job is not allowed

If no migration is allowed in the scheduling algorithm, it is considered a partitioned approach, a global approach on the other hand allows task and job migration.

### 2.1.1 Partitioned Scheduling algorithms

As mentioned before, in the partitioned approach, there is no support for job/task migration. This has a very important practical implication, as once the task has been scheduled as part of a multi-processor system, it becomes a homogeneous processor problem. Well researched algorithms [18, 19] developed for single processor scheduling can then be used.

Partition based algorithms [20, 21, 22, 23, 24] are implemented by using one run queue for each processor. This implies that if a task overruns its worst case performance, it only affects that processor. This localizes the problem and is more manageable for large systems as compared to global scheduling. However, the disadvantages of the partitioning approach to multiprocessor scheduling is that the determining the ideal number of processor required by an optimal algorithm is NP-Hard [25].

## 2.1.2 Global scheduling algorithms

In global scheduling algorithms, tasks are permitted to migrate from one processor to another. The focus of the majority of research done in this domain has been on job level migration. The goal has been to optimize the preemption and scheduling of jobs [17]. In this scheduling method, there is only one run queue for the entire system. This implies that there will be fewer context switches as compared to the partitioned method as the scheduler will preempt only when all processors are busy. The method is much more efficient as any spare processing power can be used by other jobs and not just those on the same processor.

However, the use of global scheduling algorithms was discouraged due to the Dhall effect. Dhall and Liu [26] showed that some tasks may not be schedule-able even though system is underutilized [4] and the tasks have low utilization. But, Philips et. al [27] proved that augmenting a system by increasing the processor speed is more effective than augmenting a system by increasing the number of processors. Therefore the Dhall effect only occurs when at least one task is needed with very high utilization [17, 28] thereby renewing interest in global scheduling algorithms.

An example of such algorithm is P-fair scheduling [29]. In this algorithm, all urgent tasks are scheduled first and the remaining resources are distributed to other highest priority task contending based on the total order function [29]. This algorithm was further improved in [30, 31], by optimizing the memory access patterns of tasks. They propose improving throughput by discouraging tasks that generate high memory to L2 cache traffic from being co-scheduled. This concept was further enhanced by [32] where they consider a model to find out a group of tasks that can be encouraged to be co-scheduled. The essence of the problem is to promote parallelism; therefore they propose a modified P-fair algorithm which focuses on reducing the spread (the time interval in which each job of a task is scheduled). The ideal spread would be 1, but as perfect parallelism is not always achievable, therefore they show that cache use is more efficient when the spread is minimized.

### 2.1.3 Heuristic based scheduling algorithms

### 1. Exact algorithms

(a) Algorithms that have a guaranteed solutions. These can also be the optimal solutions for a given problem

### 2. Approximation Algorithms

- (a) Algorithms that produce solutions that are guaranteed to be within a fixed percentage of the actual optimum.

- (b) Approximation algorithms are fast and have polynomial running time

### 3. Heuristic Algorithms

- (a) These algorithms produce solutions, which are not guaranteed to be close to the optimum

- (b) The performance of heuristics is often evaluated empirically

The algorithm to map a set of tasks to a set of processing elements is NP hard, therefore the only solution space available is the heuristic algorithms.

These can further be sub divided into:

### 1. Construction Heuristics [33]

- (a) The algorithm begins without a known schedule, and then adds one job at a time

- (b) Dispatching rules are examples of the construction heuristics. A *dispatching rule* is a rule that prioritizes all the jobs that are waiting for processing on a machine. Whenever a machine has been freed, a dispatching rule inspects the waiting jobs and selects the job with the highest priority

- (c) Some examples of dispatching rules are [33]

- i. Shortest Processing Time first (SPT)

- ii. Longest Processing Time first (LPT)

- iii. Earliest Completion Time first (ECT)

### 2. Improvement Heuristics [33]

- (a) The algorithm begins with a known schedule, this is considered optimum for solving the problem

- (b) The goal is to then find a better schedule similar to the one it started with, when adding a new task

- (c) Some of the examples are: Iterative Improvement, Threshold Accepting, Simulated Annealing

Construction heuristics using dispatching rules are very useful, they are simple and fast to implement and can find a reasonably good solution [33]. However, one of its biggest drawbacks is unpredictability. Therefore it is more common to use composite dispatching rules which combine multiple dispatching rules to improve the scheduling performance. In this method, a scaling parameter can also be chosen to scale the contribution of the dispatching rule. The most common rules are:

Min-min heuristic- For each component, the resource having the minimum estimated completion time (ECT) is found. Denote this as a tuple (C, R, T), where C is the task, R is the processor for which the minimum is achieved and T is the corresponding ECT. In the next step, the minimum ECT value over all such tuples is found. The task having the minimum ECT value is chosen to be scheduled next. This is done iteratively until all the tasks have been mapped. The intuition behind this heuristic is that the make span increases the least at each iterative step with the hope that the final make-span will be as small as possible.

Max-min heuristic- The first step is exactly same as in the min-min heuristic. In the second step the maximum ECT value over all the tuples found is chosen and the corresponding task is mapped instead of choosing the minimum. The intuition

behind this heuristic is that by giving preference to longer jobs, there is a hope that the shorter jobs can be overlapped with the longer job on other processors.

Sufferage heuristic: In this heuristic, both the minimum and second best minimum ECT values are found for each task in the first step. The difference between these two values is defined as the sufferage value. In the second step, the task having the maximum sufferage value is chosen to be scheduled next. The intuition behind this heuristic is that jobs are prioritized on relative affinities. The job having a high sufferage value suggests that if it is not assigned to the processor for which it has minimum ECT, it may have an adverse effect on the make-span because the next best ECT value is far from the minimum ECT value. A high sufferage value job is chosen to be scheduled next in order to minimize the penalty of not assigning it to its best processor.

## 2.2 Advances in Heterogeneous architectures

Moore's Law, which predicts that the transistor density doubles every 18 months has continuously driven improvement in hardware architectures. However, for current applications, just increasing transistor density does not deliver the same improvement in application performance. Various strategies are being investigated to overcome this problem [34]

- Multicore systems: Combining two or more cores on one die

- Simplest method to improve performance. By combining multiple cores, performance improves while reducing power/heat consumed per core

- It may not be suitable for data intensive applications

- Specialized processors : Unconventional architectures targeting high performance in specific applications

- Examples include vector processors, Digital Signal Processors(DSP) and Graphical Processing Units (GPUs)

- While these processors are very efficient for certain applications, they are not suitable for general purpose applications

- Heterogeneous architectures [35, 36]: Computing architectures in which conventional and specialized architectures work cooperatively

- This strategy combines the benefits of the above methods wherein general purpose computations are handled by the conventional processor and specific applications are accelerated by the unconventional processors

- Special programming paradigms need to be applied to take full advantage of such a system. In many cases, existing algorithms need to be redefined and implemented

Keeping the above points in mind, it can be observed that heterogeneous model is best suited for augmenting Moore's Law [34].

## 2.2.1 Heterogeneous architectures

Programming complexity has been the main barrier toward widespread adoption of heterogeneous architectures. But with the rise of disruptive technologies like the multicore/GPU architectures, scientists have adapted and modified existing algorithms to fully exploit it's advantages. There are many examples of the heterogeneous environments

### CPU-FPGA Co processor Model

Highly successful model in many applications [37, 35, 36]. The main drawback of this model is the complex programming environment (VHDL). Many C to VHDL compilers and integrated development tools have been created to alleviate this problem. Altera, FPGA manufacturer, has recently developed an OpenCL SDK [38] to reduce the programming effort and time to market.

### Cell Broadband Engine

Cell Broadband Engine (CELL BE) [39] was developed by through an alliance of IBM, Toshiba and Sony. It consists of a multi core chip composed of the Parallel Processing Element(PPE) and multiple Synergistic Processing Elements(SPE). The PPE and SPE are connected through an internal High Speed Bus and optimized for single precision floating point operations [39]. However, this technology has not been very successful due to limited support available for its programming framework.

### CPU-GPU Co-processor Model

GPUs have been used for general purpose computation for over a decade [5]. By increasing parallelism instead of frequency, GPUs have been able to improve performance while reducing power requirements. One of the drawbacks of increasing parallelism [5, 35, 36] is that it only accelerates parallel code. Sequential execution and control logic are not very efficient on the GPU. This serial section hence becomes the bottleneck during execution, thus most applications are benefited by combining multi-core CPUs and massively parallel GPUs [34]. Applications in Query co-processing [40] can especially benefit from such a architecture. It is also observed that closely coupling the CPU and GPU allows sharing of resources like memory and cache allowing greater acceleration of applications [40]

CPUs are designed to handle logical functions owing to large die area dedicated to caches and instruction level parallelism. This reduces the die are for integer and floating point calculators. This also reduces the number of cores that placed on the same die (typically 4-8). On the other hand, GPUs have much simpler cores and simpler control logic [36]. In the Fermi [41] based architecture, 512 accelerator cores are available. These cores are organized into 16 streaming multiprocessors and are clocked at roughly 1.5 GHz.

The latest GPU developed by Nvidia is the Kepler class [42]. It is divided into 4 multiprocessors with 192 cores each totaling to 1536 cores. This class of GPUs operates at a lower frequency of 1 GHz. The next generation 28 nm production process coupled with lower operating frequency drastically lowers the power consumption. ling to 1536 cores. This class of GPUs operates at a lower frequency of 1 GHz. The next generation 28 nm production process coupled with lower operating frequency drastically lowers the power consumption.

# 2.3 Scheduling algorithms in heterogeneous architectures

As described in the section 2.1, scheduling algorithms for homogeneous architectures has been well explored. While scheduling in heterogeneous architectures has also been covered well, it has mainly been restricted to distributed and grid systems [43, 44, 45]. The research in this area for heterogeneous architectures like the GPUs within a single machine has only picked over the last five years [46, 12, 47, 3, 48] due to improvement in architecture technology. Due to the specialization of GPU hardware, there are more considerations that need to be taken into account for [4], such as:

- Computing model of task, either adapted to CPU or GPU

- Amount of computing resources

- Difference in the memory architecture of the GPU

- Bottleneck of data transfers between CPU and GPU

A simple method was presented by Wang et al. [4], where tasks are divided into two categories, computing tasks and communicating tasks. A hierarchical control data flow is constructed where computing tasks are operating nodes and communicating tasks are transmitting nodes. Using this task partitioning and execution runtime of tasks, the algorithm decides which processing element the task runs on. The method proposed is very simplistic and vague; the authors compare their solution with a traditional method and claim about 23% improvement in performance. However details of the comparison are not well documented.

In the method proposed by Jiménez et al. [43], a predictive user level scheduler is used which schedules tasks based on previous performance on a CPU and a GPU. This algorithm is further elaborated in section 2.4.2. The Harmony framework [49] which is analyzed in section 2.4.1 represents programs as a sequence of kernels. This framework considers scheduling of these kernels based on the suitability of the kernels towards a particular architecture. Using a multivariate regression model, they dynamically assign different tasks to the processing elements. The Qilin framework [48] on the other hand predicts run time using similar regression models offline. After extensive profiling of tasks offline, using different input parameters, a linear model is created. This method however may not be suitable for all applications and in some cases may require extensive profiling. MapReduce is a programming model that enables massive data processing in large scale computing environments. This model can take advantage of the superior performance of GPUs. One such framework which considers task scheduling is illustrated by Shirahata et al. [47]. The industry standard Hadoop framework [50] is used and extended to invoke CUDA functions. The authors suggest an approach that optimizes the schedule based on

minimizing the elapsed time. Task profiles are collected using heartbeat messages. At 64 nodes (best configuration) this method improves performance by 1.93 times but suffers significant overhead due to the Hadoop map task invocation.

MARS [51] is another MapReduce framework implemented using GPUs to speed up many web applications. However, one drawback of using the MapReduce solution on the GPU is that of memory. GPUs have comparatively lesser memory and may not be sufficient to solve larger web based problems which have generally process gigabytes or terabytes of data. Therefore more experiments need to be conducted to get more quantitative results.

A dynamic approach to schedule tasks was proposed by Ravi et al. [3] for MapReduce problems. Programs are divided into chunks which are then distributed across the devices. This method is beneficial as it requires minimum input from users and does not use any profiling techniques. The general idea of this algorithm is straightforward as it uses a master-slave model to allocate new chunks once the processing elements complete their previous work. However, one of the drawbacks of this framework is the choice of chunk size. Their experimental results show a high variation in performance when different sizes are chosen. Choosing the optimal size has been left for further research [3].

Grewe et al. [46] used OpenCL and Clang [52] frameworks to analyze programs and extract static code features to partition these programs across devices. The key contribution of this work is a machine learning based compiler that accurately predicts the best partitioning of a task using these static code features. A two-level predictor is used to partition the tasks. This is a fine grained approach to solve the scheduling problem but according to the authors themselves most of the programs are scheduled by the level one predictor. This calls to question the need for an extensive second level predictor. Also choice of features has not been justified and any changes in the static features will require re-training the entire model which can be quite laborious as machine learning algorithms are computationally expensive.

However, their approach is unique, wherein task partitioning is considered instead of scheduling between a CPU and GPU. A detailed analysis of the same is conducted in section 2.4.3.

# 2.4 Current models and frameworks for CPU-GPU environment

In this section, some of the current models and interesting ideas that the author finds relevant to his study will be presented.

### 2.4.1 Harmony Model

The Harmony model [49] is a runtime supported programming and execution model which is concerned with simplifying development and ensuring binary portability and scalability across different system configurations. The model provides

- Semantics for simplifying parallelism management

- Dynamic scheduling of compute intensive kernels

- Online monitoring based optimization for heterogeneous systems

This model is divided into two sections namely programming model and execution model.

### Harmony programming model

The programming model is relatively simple: it consists of compute intensive kernels (analogous to function calls), whose execution is managed by control decisions. The control decisions take in a set of input variables and determine the next kernel to be executed. As kernels are encountered, there are dispatched via blocking calls. Kernel arguments are managed by using a shared address space. These are treated as global variables by the runtime.

### Harmony execution model

During execution, an application dispatches kernels via the Harmony API which is registered by the API along with its dependence information. Kernels in the dispatch window are then scheduled on cores for which the binaries exist. It optimizes the schedule by using speculative kernel execution. When an application is run via the API, it first scans the kernels in the dispatch window without blocking. This allows it to build a graph which represents all the data dependencies between the kernels. Control decisions determine the number of kernels that can be scanned without blocking. Non flow dependencies are removed by variable renaming. As the kernels complete execution, the dispatch window and schedule are updated. The harmony model shows promising results, for a matrix multiplication application it can transparently transfer it to the GPU as the size of the matrix increases. However it does not really propose any new heuristic for task scheduling. It relies on the control decisions specified to make a choice between different architectures.

But on the other hand, it provides a simple model for effectively using a CPU and a GPU. As the model is generic it can also be extended to other architectures like FPGA's as long as the corresponding binary is present. This makes it an ideal runtime framework for different heterogeneous architectures.

### 2.4.2 Predictive runtime scheduling

In this work by Jimenez et. al [43], a novel predictive user level scheduler based on the past performance history is presented. The authors envision a state of the art heterogeneous system where all processing elements are utilized by different applications (not just scientific) and are able to adapt their behavior to improve execution time. In the model, function level granularity is chosen; the scheduler is used as a library in the Linux OS. It is implemented as process level scheduler. This is done as developing it as a kernel level scheduler poses difficulties and involves a long development time. Therefore the interface to the scheduler is a set of C++ classes. There are two steps in the algorithm namely Processing Element (PE) selection and task selection.

### **Processing Element Selection**

In this step, the PE on which a task should be executed is selected. This does not mean that execution begins immediately but is a mechanism to choose which task is best suited for a particular PE. There are two alternatives developed for this step. One method uses the First-Free heuristic which is scheduling the tasks on the first available PE. However this technique is not very efficient therefore a predictive algorithm based on past performance was developed. In this method, a performance history is maintained for all PE and task pairs by forcing the first N calls of the same function to N different PEs. The next function call is then scheduled according best possible execution time.

### Task Selection

All algorithms in this step follow the First Come First Serve heuristic. This is one of the main drawbacks of this work as it does not consider any load balancing techniques and may not always be optimum.

### **Evaluation**

In order to evaluate their work, the authors have used a mix of synthetic and real benchmarks namely matmul, ftdock, cp and sad. Even though First Free heuristic is simple, it shows considerable improvement in some of the benchmarks. In some cases, it claims about 60% improvement in performance. But in other cases the improvement is insignificant or even degraded. This could be because some benchmarks are biased towards one

PE. There are two variations of the predictive algorithms implemented, namely history-gpu and estimate-hist. Both the algorithms look at the performance history and create an 'allowed-pe' list. In the next step history-gpu schedules the task to first available allowed-pe while estimate-hist estimates the waiting time on all PEs and schedules the task to the PE with lowest waiting time. Both these algorithms show more consistent and significant speedups. history-gpu performs better as the number of PE are increased but estimate-hist manages to balance workload between CPU and GPU better.

### **Analysis**

This model presents a simple scheduler to optimize performance on heterogeneous architectures. As it is implemented as a library, it can also be extended to other architectures. It shows significant improvement over just using the CPU or GPU and is able to fully utilize both the processing elements. However, because of its simple nature, there is reduction in speedup when the number of tasks that need to be scheduled is increased. Being a user level scheduler, there is also interference from other OS level tasks. This can also degrade performance. Another shortcoming of this method is that they haven't explicitly considered the data transfer time between the CPU and GPU which is significant in many cases.

## 2.4.3 Static Partitioning using OpenCL

This work [46] presents a static partitioning approach to scheduling tasks/jobs to a heterogeneous environment like the CPU and GPU. The OpenCL environment is used to analyze programs and extract static code features. They claim the static approach is superior as it does not require any offline profiling and also avoids the overheads of a dynamic run time solution. The key contribution of this paper is a machine learning based compiler that accurately predicts the best partitioning of a task using static code features. They have used over 47 benchmarks which are friendly towards both CPU and GPU to validate their claim. The static code features are extracted using Clang [52]. The OpenCL code is read by Clang which builds an abstract syntax tree. This is used to analyze the code and extract features such as number of floating point operation or number of memory accesses. Similar features such as memory access are coalesced and a Principal Component Analysis (PCA) is done to reduce the dimensionality of the feature space before the results are fed into the model.

### **Training Data**

The training data used in this work are the static code features of OpenCL programs and their optimal partitioning. The former is the input and the latter is the output. Using these, a model is created. Each program is run in varying partitions, namely all work on (CPU, GPU), (90% on CPU 10% on GPU) and so on. The partitioning with the lowest runtime is selected as the ideal partitioning.

#### Predictor

All OpenCL programs can be classified into three categories, namely

- 1. Executed only on CPU

- 2. Executed only on GPU

- 3. Partitioned and distributed between CPU and GPU

In order to predict the correct partition, a two level hierarchical predictor is presented. In the first level, programs belonging to category one and two are filtered and scheduled to the corresponding devices. Therefore the features here are reduced to two using PCA. The remaining programs are then mapped according to third predictor. Here the features are reduced to 11 classes; class 0 represents GPU only while class 10 represents CPU only. All other classes represent a mix of the two.

#### Results

In this implementation, majority of the programs are filtered out by the first level predictor, only few programs required a more fine grained approach to partitioning. All comparisons of speedup are made with the performance of a single core system. The proposed approach is then compared with static strategy of CPU only, GPU only and the dynamic approach proposed by Ravi et al [3].

### GPU friendly benchmarks

In these benchmarks, for obvious reasons the GPU only approach achieves the best performance. The CPU only approach loses in these benchmarks. The results of the dynamic approach [3] are good but lose out, as some of the work is performed on the CPU, this degrades performance as compared to GPU only approach. The prediction approach proposed correctly predicts for all programs and they are scheduled on the GPU thereby achieving optimal performance.

### CPU friendly benchmarks

In these benchmarks, CPU only approach achieves the best performance and a speedup of 6.12. GPU only achieves a speedup of 1.05 for obvious reasons. The dynamic approach also performs badly as it suffers from overheads of transferring data to the GPU when it is actually inefficient to do so. The partitioning approach performs slightly better and is able to achieve a speedup 4.81.

### Remaining Benchmarks

In these benchmarks, the static approaches perform the worst with a speedup 4.49(CPU) and 6.26 (GPU) as the optimal performance is achieved only when the work is distributed. The dynamic approach shows a lot of potential here and achieves a speedup of 8. The partitioning approach gives an even better performance and achieves a speedup of 9.31 as it does not suffer from the scheduling overheads.

### Analysis

The work in this paper is very well presented. It shows that the partitioning approach can outperform the scheduling approach. Their method of validating their claim by using benchmarks friendly to CPU, GPU and also a mixture gives a better perspective on their result as compared to other works [43, 49]. However this method is a fine grained approach to solve the scheduling problem. According to the authors themselves most of the programs are scheduled by the level one predictor. This calls to question the need for an extensive second level predictor. Apart from that, training the model can be quite laborious as machine learning algorithms are computationally expensive. Also choice of features has not been justified and any changes in the static features will require retraining the entire model.

## 2.5 Summary

This chapter introduced the basics of scheduling in a parallel environment. It highlighted the need for classifications of scheduling algorithms based on the type of architectures they support. Section 2.1 illustrated the different algorithms used on homogeneous architectures. It introduced the two types of scheduling algorithms based on the level of job migration allowed. Both these methods namely the Partitioned approach and Global scheduling approach were elaborated and the benefits and problems of the two were discussed. The current state of the art in scheduling tasks in heterogeneous architectures was introduced in section 2.3. It also highlighted the need to use different types of strategies due to the nature of the architectures. Many algorithms and their competencies were discussed in this section. Section 2.4 then elaborated on the chosen few models/frameworks that this author felt was relevant to his study. The pros and cons these models were also discussed. Therefore in conclusion, while there is a wealth of literature on the subject, there is still a search for an optimal algorithm. Many considerations like optimizing memory transfers along with task scheduling, fine grained vs. coarse granied scheduling and optimization of device utilization can still be studied.

# Chapter 3

# **Programming Framework**

## 3.1 Introduction

In order to accelerate an application using a GPGPU solution, there are many programming options available. The most commonly used Application Programming Interfaces (API) are CUDA (Compute Unified Device Architecture), OpenCL [53] (Open Computing Language) and DirectCompute. DirectCompute is a GPGPU API developed by Microsoft which uses High Level Shader Language (HLSL) syntax. It is easy to use for existing DirectX programmer but otherwise has very little support and documentation.

OpenACC is another programming standard for parallel computing developed by Cray, CAPS, Nvidia and PGI. The standard is designed to simplify parallel programming of heterogeneous CPU/GPU systems [54]. Similar to OpenMP, sections of C/Fortan code can be identified and accelerated using PRAGMA compiler directives and additional functions. Unlike OpenMP, code can be started not only on the CPU, but also on the GPU. The directives and programming model defined in the OpenACC API document allow programmers to create high-level host + accelerator programs without the need to explicitly initialize the accelerator, manage data or program transfers between the host and accelerator, or initiate accelerator start-up and shutdown [54].

CUDA is a more mature framework developed by Nvidia. It has a C like syntax making it easier to program for existing C programmers. It provides excellent support for different GPU optimized libraries and integrates easily into existing solutions. However, CUDA is only supported by Nvidia GPUs. This is the main drawback; it does not even fall back to CPU if a GPU is not detected.

StarPU [55, 1] is a runtime system capable of scheduling tasks over heterogeneous, accelerator based machines. It is a portable system that automatically schedules a graph of tasks onto a heterogeneous set of processors. It is a software tool aiming to allow programmers to exploit the computing power of the available CPUs and GPUs, while relieving them from the need to specially adapt their programs to the target machine and processing units. StarPU's run-time and programming language extensions support

a task-based programming model. Applications submit computational tasks, with CPU and/or GPU implementations, and StarPU schedules these tasks and associated data transfers on available CPUs and GPUs. The data that a task manipulates are automatically transferred among accelerators and the main memory, so that programmers are freed from the scheduling issues and technical details associated with these transfers. This framework is further elucidated in Section 3.3.

## 3.2 OpenCL Application Programming Interface

OpenCL is an open source API developed to enable co-processors to work in tandem with CPUs which is maintained by the Khronos group. It is supported by many companies like ADM, Nvidia, Intel and ARM holdings. It is similar to CUDA as it also has a C like syntax and can be integrated easily. The main advantage of OpenCL is that it supports multiple devices. Some examples are multi-core CPUs, multi-socket CPU, GPUs and Cell processors.

This means that a programmer can change the hardware architecture without any changes to the code as OpenCL is a standard from which vendors are expected to derive abstractions to support their devices. Therefore it can in theory support many more devices like FPGAs and mobile hardware in the future [2]. The ability to support a general heterogeneous environment and wide industry support has been the motivation to choose this API for the remainder of the project.

Each OpenCL implementation (i.e. an OpenCL library from AMD, NVIDIA, etc.) defines platforms which enable the host system to interact with OpenCL-capable devices. The software architecture of all implementations can be described by:

- Platform Model

- Execution Model

- Memory Model

### 3.2.1 Platform Model

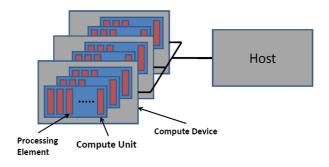

The platform model consists of a host connected to one or more OpenCL devices [2]. A device is divided into one or more compute units. Compute units are divided into one or more processing elements. This hierarchy is described in the Figure 3.1. Each processing element is executes independently as it maintains its own program counter.

### 3.2.2 Execution Model

The execution model of the OpenCL API [53] is defined by two parts namely kernels that execute on one or more OpenCL devices and a host program that executes on the host.

Figure 3.1: OpenCL platform model [2]

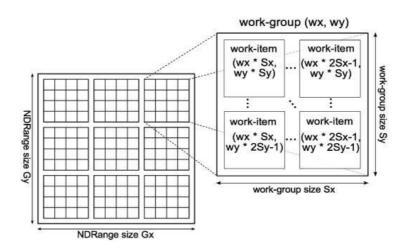

The host program defines the context for the kernels and manages their execution. When a kernel is submitted for execution by the host, an index space is defined. The index space supported in OpenCL 1.0 is called an NDRange. An NDRange is an N-dimensional index space, where N is one, two or three. It is defined by an integer array of length N specifying the extent of the index space in each dimension.

An instance of the kernel executes for each point in this index space. This kernel instance is called a work-item and is identified by its point in the index space, which provides a global ID for the work-item. Each work-item executes the same code but the specific execution pathway through the code and the data operated upon can vary per work-item. Work-items are organized into work-groups. The work-groups provide a more coarse-grained decomposition of the index space. As shown in figure 3.2, work-groups are assigned a unique work-group ID with the same dimensionality as the index space used for the work-items [53]. All work items in a workgroup execute together on the same compute unit, thereby sharing local memory. Only work items in the same work group can be synchronized. The size of the work groups is called the local work-size of the kernel

Figure 3.2: Work-item/Work-group example [2]

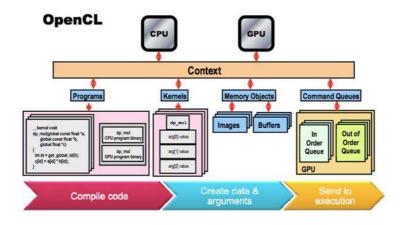

#### Context

The host defines a context for the execution of the kernels. The context includes the following resources:

- Devices: The collection of OpenCL devices to be used by the host.

- Kernels: The OpenCL functions that run on OpenCL devices.

- Program Objects: The program source and executable that implement the kernels.

- Memory Objects: A set of memory objects visible to the host and the OpenCL devices.

The context is created and manipulated by the host using functions from the OpenCL API. The host creates a data structure called a command-queue to coordinate execution of the kernels on the devices.

#### **Command Queues**

The host places commands into the command-queue which are then scheduled onto the devices within the context. These include:

- 1. Kernel execution commands: Execute a kernel on the processing elements of a device.

- 2. Memory commands: Transfer data to, from, or between memory objects, or map and un-map memory objects from the host address space.

- 3. Synchronization commands: These commands constrain the order of execution. The command-queue schedules commands for execution on a device. These execute asynchronously between the host and the device. Commands execute relative to each other in one of two modes:

- (a) In-order Execution: Commands are launched in the order they appear in the command queue and complete in order. This serializes the execution order of commands in a queue.

- (b) Out-of-order Execution: Commands are issued in order, but do not wait to complete before the following commands execute. Any order constraints are enforced by the programmer through explicit synchronization commands. Kernel execution and memory commands submitted to a queue generate event objects. These are used to control execution between commands and to coordinate execution between the host and devices.

It is possible to associate multiple queues with a single context. These queues run concurrently and independently with no explicit mechanisms within OpenCL to synchronize between them.

## 3.2.3 Memory Model

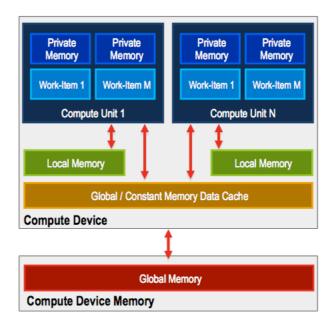

Work-items executing a kernel have access to four distinct memory regions as shown in Figure 3.3. Each region has a specific purpose. Memory objects can be accessed by all devices only when they are defined in the same context. The different classifications are:

Figure 3.3: OpenCL memory model [2]

- 1. Global Memory: This memory region permits read/write access to all work-items in all work-groups. Work-items can read from or write to any element of a memory object.

- 2. Constant Memory: A region of global memory that remains constant during the execution of a kernel. The host allocates and initializes memory objects placed into constant memory.

- 3. Local Memory: A memory region local to a work-group. This memory region can be used to allocate variables that are shared by all work-items in that work-group. It may be implemented as dedicated regions of memory on the OpenCL device. Alternatively, the local memory region may be mapped onto sections of the global memory.

- 4. Private Memory: A region of memory private to a work-item. Variables defined in one work-item's private memory are not visible to another work-item.

# 3.2.4 Summary

As shown in Figure 3.4, the OpenCL framework consists of program code which runs on the Host device, kernel programs which can run on all OpenCL capable devices defined within the same context. Work packages are enqueued by the framework to a device and executed either in-order or out-of-order. Memory management on the other hand needs to be done manually using the different types of memory objects mentioned above. However, OpenCL is still an ongoing project and is gradually being embraced by many hardware vendors and may undergo changes in the future.

Figure 3.4: Complete OpenCL framework [2]

# 3.3 StarPU Scheduling Interface

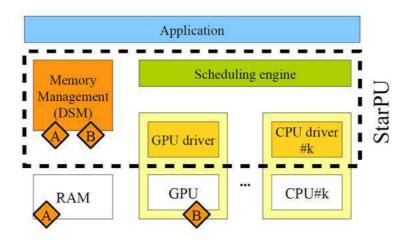

StarPU [55], developed by INRIA, is a runtime system capable of scheduling tasks over heterogeneous, accelerator based machines. It is a portable system that automatically schedules a graph of tasks onto a heterogeneous set of processors. It is a software tool aiming to allow programmers to exploit the computing power of the available CPUs and GPUs, while relieving them from the need to specially adapt their programs to the target machine and processing units. Many applications like the linear algebra libraries MAGMA [56] and PaStiX [57] use StarPU as a backend scheduler for deployment in a heterogeneous environment. Taking into account the extensive use of StarPU in such applications, it is an ideal choice as a scheduler for this investigation. Applications submit computational tasks, with CPU and/or GPU implementations, and StarPU schedules these tasks and associated data transfers on available CPUs and GPUs. The data that a task manipulates are automatically transferred among accelerators and the main memory, so that programmers are freed from the scheduling issues and technical details associated with these transfers [55]. StarPU maintains the historical data of application runtimes over different data-sizes and builds performance models for each device. It uses these auto-tuned models along with well-known algorithms like HEFT (Heterogeneous Earliest Finish Time), WS (Work Steal) and other variants for scheduling tasks efficiently. In most cases, these algorithms are sufficient; however custom scheduling techniques can also be defined.

The next two sections provide an overview of the StarPU framework, it is not intended to be an extensive tutorial but aims to provide a basic understanding of the framework and how scheduling decisions are made.

# 3.3.1 Programming Interface [1]

The programming interface of StarPU can be described using the following data structures:

- 1. Codelets: This data structure is used to describe the computational kernels that can be implemented on different architectures. It also defines the data buffers and the data access rules (READ/WRITE) that are used by the kernels.

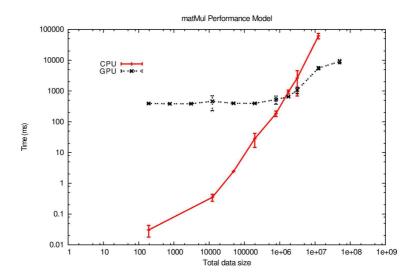

- (a) Each codelet can be associated with a performance model. These models can take into consideration execution time by the performance model as well as power consumption. These models are built using the execution profile of the application over at least 10 iterations. Every time the application is run, its execution profile is saved and the model is updated using hashing techniques. Alternatively, by specifying different parameters during the execution ,these models can also be derived using regression based estimates and are used by StarPU to make scheduling decisions. An example of a performance model is shown in figure 3.5. It describes the performance on a CPU and a GPU for a 2D matrix multiplication codelet.

Figure 3.5: Performance model of Matrix Multiplication

- 2. **Task**: The task is an instantiation of a codelet. This structure is used to apply a codelet on a data set, on the architectures for which the codelet is defined. The StarPU GCC plug-in views tasks as Extended C functions.

- (a) Tasks may have several implementations, one for each device

- (b) Tasks may have several implementations of the same device. When invoked, StarPU can choose any of its implementations.

- (c) Data handles that are used to describe the data set that each task uses. These handles need to be registered with StarPU and are used to data management between different devices

- (d) Callback functions can be defined for each task, these are invoked after the successful completion of the task

- (e) Other additional options like task dependencies and priority levels can also be specified using this structure

- (f) The task can also be defined as synchronous or asynchronous, which means that the task will only be executed in the order of submission. However, the process of task submission itself is always asynchronous (non-blocking operation).

By default, task dependencies are inferred from data dependency (sequential coherence) by StarPU. The application can however disable sequential coherency for some data, and dependencies be expressed by hand. A task is identified by a unique 64-bit number chosen by the application which is referred to as a tag. Task dependencies can be enforced either by the means of callback functions or by expressing dependencies between tags of tasks that have not been submitted yet.

# 3.3.2 Task Scheduling [1]

StarPU obtains performance portability by efficiently using all computing resources at the same time. It provides a unified view of all computational units and can effectively map tasks in a heterogeneous environment while transparently handling low level function like data transfer automatically. Also, by comparing the relative performance of tasks on different processing units, processing units can automatically execute the tasks they are best suited for.

#### Data Management

Data that is manipulated by the different devices needs to be registered with the StarPU scheduler through the  $starpu\_data\_handle()$  data structure. Using these data handles it automatically manipulates all data transfers between the devices. StarPu replicates data on all devices and by default, stores these wherever they were used. This is to ensure minimal data transfer overhead in case they are re-used by other tasks on the same device. When a task modifies some data, all other copies are invalidated, and only the device which ran that task has a valid replicate of the data.

#### Task Submission

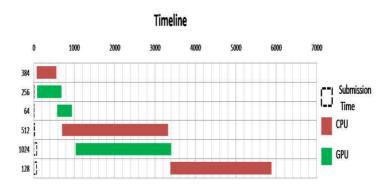

The  $starpu\_create\_task()$  function is used to create tasks. Once the appropriate data fields are filled, it can be submitted to the scheduler using the  $starpu\_task\_submit()$  function. This operation can be completely asynchronous by setting the appropriate flag during task creation. In the ideal case, all tasks should be submitted asynchronously. The  $starpu\_wait\_for\_task()$  or

starpu\_task\_wait\_for\_all() functions should be used to wait for tasks to terminate. StarPU will then be able to rework the whole schedule, overlap computation with communication and manage accelerator local memory usage. Figure 3.6 shows an example of multiple tasks being submitted asynchronously and scheduled using the work-steal algorithm by StarPU across different processing elements.

Figure 3.6: Execution timeline of multiple tasks

#### Task scheduling algorithms

#### Performance modeling

Performance modeling is the key to scheduling tasks effectively on StarPU. The application programmer needs to configure a performance model for the codelets of the task. There are two types of models available namely  $STARPU\_HISTORY\_BASED$  and  $STARPU\_REGRESSION\_BASED$ .  $STARPU\_HISTORY\_BASED$  measures runtime performance. This assumes that for a given set of data input/output sizes, the performance will always be about the same. This is very true for regular kernels on GPUs for instance (< 0.1% error) and CPUs (1% error) [1]. Records of the average run-time of previous executions on the various processing units are stored and used for estimation. This method is very useful as it has lower overhead while making scheduling decisions. However, it inherently assumes that the execution time changes based only on size of the data.  $STARPU\_REGRESSION\_BASED$  models performance based on run-times but further refined by regression. Performance regularity is still assumed, but works with various data input sizes, by applying regression over observed execution times.  $STARPU\_REGRESSION\_BASED$  uses  $a*n^b$  regression form. While this method is more

refined and accurate, it is computationally expensive. The task must also be issued multiple times with varying size as there is at least 10% difference between the minimum and maximum observed input size for regression to be accurate. Overall, both methods require a minimum of 10 measurements on each device before the scheduler starts to trust the performance models.

#### Scheduling algorithms

Performance models are required by most scheduling algorithms in order to make intelligent decisions while scheduling different tasks. By default, StarPU uses the *eager* simple greedy scheduler. This is because it does not need performance models for scheduling. Other algorithms that do not need performance models are:

- 1. The eager scheduler uses a central task queue from which devices draw task to work on. This however does not permit it to pre-fetch data since the scheduling decision is taken late. If a task has a non-0 priority, it is put at the front of the queue.

- 2. The Prio scheduler also uses a central task queue but sorts tasks by priority (between -5 and 5).

- 3. The random scheduler distributes tasks randomly according to assumed overall device performance.

- 4. The WS (Work Stealing) scheduler schedules tasks on the local device by default. When another device becomes idle, it steals a task from the most loaded device.

If performance models are available, other scheduling algorithms can be used by StarPU, namely

- 1. The DM (Deque Model) scheduler uses task execution performance models into account to perform an HEFT-similar scheduling strategy: it schedules tasks where their termination time will be minimal.

- 2. The DMDA (Deque Model Data Aware) scheduler is similar to DM, it also takes into account data transfer time.

- 3. The DMDAR (Deque Model Data Aware Ready) scheduler is similar to DMDA, it also sorts tasks on per-worker queues by number of already-available data buffers.

- 4. The DMDAS (Deque Model Data Aware Sorted) scheduler is similar to DMDA, it also supports arbitrary priority values.

- 5. The HEFT (Heterogeneous Earliest Finish Time) scheduler is similar to DMDA, it also supports task bundles.

- 6. The Pheft (parallel HEFT) scheduler is similar to HEFT, it also supports parallel tasks (still experimental).

- 7. The PGreedy (Garallel Greedy) scheduler is similar to Greedy, it also supports parallel tasks (still experimental).

## 3.3.3 Summary

StarPU is an open source scheduler that can be used to schedule tasks in a heterogeneous environment. It massively reduces the amount of data transfers without any application code modification. The unique selling point of StarPU is the tight collaboration between its high-level data management library and its portable scheduling engine. This allows the programmer to easily design powerful scheduling policies. An overview of the StarPU execution model is shown in Figure 3.7. StarPU unlocks the portability of performance on complex accelerator-based platforms: it is for instance generic enough to transparently handle heterogeneous multi-GPU setups by hiding both low-level heterogeneity and by dispatching tasks according to the capabilities of the different units. StarPU is not limited to multi-core machines equipped with GPUs and Cell processors. Its asynchronous event-driven design will for instance make it straightforward to implement an OpenCL backend.

Figure 3.7: Execution model of StarPU [1]

# Chapter 4

# Fine Grained Scheduling

## 4.1 Introduction

As mentioned in Chapter 1, introduction of heterogeneous architecture has led to an immense improvement in performance at lower cost. While many applications can take advantage of the superior performance, programming them efficiently is still a topic of active research.

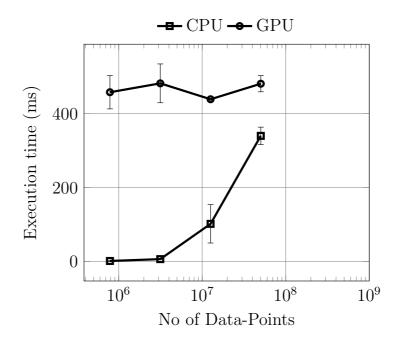

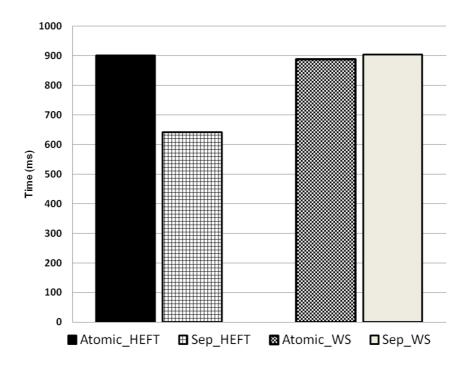

Applications like image-filtering, face recognition, gesture recognition and audio processing are multi-step processes. There are cases when certain steps within such applications may have skewed performance on a single device. In problems involving multi-step applications, it is crucial to determine which sections are more efficient on a particular device as it allows a fine grained approach to scheduling tasks. The focus here is not on partitioning the tasks themselves, but determining how such a fine grained scheduling improves overall execution time and reduces task starvation. Work Steal (WS) and Heterogeneous Earliest Finish Time (HEFT) [58] are ideal for comparison as they represent the different scheduling perspectives. Work Steal is a greedy algorithm that schedules tasks as and when a processing element becomes available, it does not take into account the historical performance on different devices.

The main idea behind Work Steal is to improve device utilization. On the other hand HEFT [58],can use performance models and historical data to make a quicker decision on ideal mapping of tasks onto devices while trying to reduce overall make-span. However, it may not be a fair algorithm as it can starve some tasks in order to run them on a better suited device leading to poor device utilization. The following sections describe in detail the effect of fine grained scheduling across the two scheduling algorithms using the StarPU framework. It also shows the result when executing applications over different data sizes.

# 4.2 Multi-step Applications

Applications, especially in the image processing domain have similar base functions. For example, several image filtering algorithms utilize the Fourier domain (and hence FFT) for faster processing. Hence, different applications can reuse come computation kernels. The matrix transpose kernel, for example is the same for the FFT and the Recursive Gaussian tasks. Other tasks like 2D matrix multiplication or matrix-vector multiplication are also used regularly as sub-tasks within a larger algorithm. Keeping this in mind, three multi-step applications were developed and used to evaluate the fine grained approach. All examples have two variations, one deployed as an atomic task and the other as non-atomic tasks. The experimental setup for these tests is mentioned in Appedndix A

## 4.2.1 Example 1

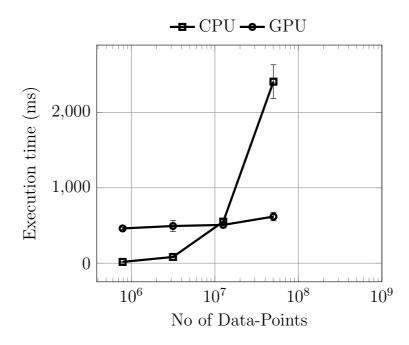

The first example used is matrix multiplication (matMul) followed by a matrix-vector multiplication (vectMul). Two variants of this application were created. mvmAtomic, is a straightforward variation, where only one task is created. The OpenCL kernels for the two sub-sections are combined and only one OpenCL execution call is made. For the other variant, mvmSep, two tasks are created and submitted to the StarPU scheduler asynchronously. An explicit dependency is specified such that vectMul is executed only after matMul. Table 4.1 shows the execution time of the tasks for different data sizes. It can be seen that the vectMul task is more efficient on the CPU even as the data size increases; while matMul is more efficient on the GPU only when the data processed is large. This is an ideal example that can be used to represent non-uniform performance within a single task.

| Tasks         |     | 256 | 512  | 1024  |

|---------------|-----|-----|------|-------|

| matMul        | CPU | 174 | 1824 | 54528 |

|               | GPU | 564 | 1011 | 5396  |

| vectMul       | CPU | 1   | 2    | 8     |

|               | GPU | 403 | 402  | 419   |

| $mvm\_atomic$ | CPU | 178 | 1436 | 54216 |