# Hardware Acceleration of the Trace Transform for Vision Applications

Suhaib A. Fahmy

This thesis is submitted for the degree of

Doctor of Philosophy of the University of London

and for the Diploma of Imperial College

Department of Electrical and Electronic Engineering

Imperial College London

University of London

December 2007

### Abstract

Computer Vision is a rapidly developing field in which machines process visual data to extract some meaningful information. Digitised images in their pixels and bits serve no purpose of their own. It is only by interpreting the data, and extracting higher level information that a scene can be understood. The algorithms that enable this process are often complex, and data-intensive, limiting the processing rate when implemented in software. Hardware-accelerated implementations provide a significant performance boost that can enable real-time processing.

The Trace Transform is a newly proposed algorithm that has been proven effective in image categorisation and recognition tasks. It is flexibly defined allowing the mathematical details to be tailored to the target application. However, it is highly computationally intensive, which limits its applications. Modern heterogeneous FPGAs provide an ideal platform for accelerating the Trace transform for real-time performance, while also allowing an element of flexibility, which highly suits the generality of the Trace transform. This thesis details the implementation of an extensible Trace transform architecture for

vision applications, before extending this architecture to a full flexible platform suited to the exploration of Trace transform applications. As part of

the work presented, a general set of architectures for large-windowed median

and weighted median filters are presented as required for a number of Trace

transform implementations. Finally an acceleration of Hidden Markov Model

decoding for person detection is presented. Such a system can be used to extract frames of interest from a video sequence, to be subsequently processed

by the Trace transform.

All these architectures emphasise the need for considered, platform-driven design in achieving maximum performance through hardware acceleration.

# Acknowledgements

I would like to thank my supervisor, Professor Peter Cheung for his guidance and support throughout this PhD. He has often gone out of his way to offer support outside of his academic duties, and for this I am grateful. I am also indebted to Dr. Christos Bouganis for his time, advice and mentoring throughout my work. Professor Wayne Luk has provided significant contributions and feedback for my publications and thesis. I would also like to thank Pete Sedcole for being there when I needed to bounce ideas off someone, and providing advice during the writing of this thesis. I received much appreciated counsel from many sources during the write-up as well as the work itself. Thanks to Alastair Smith, Ben Cope, Altaf Gaffar, Sherif Yusuf, Jon Clarke, Kieron Turkington, George Constantinides, Nick Campregher and others I may have failed to mention by name.

I cannot fail to thank my beloved wife for her patience and support over three and a half years of dealing with PhD Syndrome. My three wonderful children, Hafsah, Talhah and Yahya, have interspersed this PhD with moments of sheer joy and happiness. I apologise for the times I couldn't be there, even if, perhaps, I was in body.

I also owe a debt of gratitude to my parents for their support throughout my studies and before. And my dad for understanding the pressures of writing-up having done it himself 28 years ago.

Yet above and beyond all, and without Whom there would be no-one to thank in the first place, I praise God, the Almighty and thank Him for surrounding me with such great people and providing me with opportunities, endless as they are. There are many, the world over who will never taste these opportunities and who will pass away having never felt fulfilment. May we always be grateful for what we have, and show compassion for those less fortunate than ourselves.

# Contents

| 1 | Intr | oducti | ion                                  | 17 |

|---|------|--------|--------------------------------------|----|

|   | 1.1  | Thesis | s Outline                            | 21 |

|   | 1.2  | Contri | ibutions                             | 23 |

|   | 1.3  | Public | eations                              | 25 |

| 2 | Bac  | kgroui | nd                                   | 27 |

|   | 2.1  | Introd | luction                              | 27 |

|   | 2.2  | Field  | Programmable Gate Arrays             | 28 |

|   |      | 2.2.1  | Logic and Routing                    | 33 |

|   |      | 2.2.2  | Reconfigurability                    | 35 |

|   |      | 2.2.3  | Embedded Memories                    | 36 |

|   |      | 2.2.4  | Embedded Multipliers and DSP Blocks  | 37 |

|   |      | 2.2.5  | Other Resources                      | 38 |

|   |      | 2.2.6  | The FPGA Design Flow                 | 39 |

|   |      | 2.2.7  | Circuit Measurement Metrics          | 46 |

|   | 2.3  | Hardw  | vare Acceleration of Vision Systems  | 49 |

|   |      | 2.3.1  | Colour to Black and White Conversion | 49 |

|   |      | 2.3.2  | Object Detection                            | 51 |

|---|------|--------|---------------------------------------------|----|

|   |      | 2.3.3  | Object Segmentation                         | 52 |

|   |      | 2.3.4  | Object Tracking                             | 53 |

|   |      | 2.3.5  | Literature Summary                          | 54 |

|   | 2.4  | Summ   | ary                                         | 61 |

| 3 | Trac | ce Tra | nsform Theory                               | 63 |

|   | 3.1  | Introd | uction                                      | 63 |

|   | 3.2  | The R  | adon Transform                              | 64 |

|   |      | 3.2.1  | Mathematical Foundations                    | 64 |

|   |      | 3.2.2  | Applications                                | 68 |

|   |      | 3.2.3  | Application to Image Processing             | 71 |

|   | 3.3  | The H  | ough Transform                              | 72 |

|   | 3.4  | The T  | race Transform                              | 74 |

|   |      | 3.4.1  | Triple Feature Extraction                   | 76 |

|   |      | 3.4.2  | Selection of Functionals                    | 77 |

|   | 3.5  | Trace  | Transform Applications                      | 78 |

|   |      | 3.5.1  | Image Database Search                       | 78 |

|   |      | 3.5.2  | Token Verification                          | 81 |

|   |      | 3.5.3  | Change Detection                            | 81 |

|   |      | 3.5.4  | Face Authentication                         | 83 |

|   | 3.6  | Comp   | utational Complexity of the Trace Transform | 86 |

|   | 3 7  | Relate | ed Hardware Implementations                 | 90 |

| ti   | ons 95                                                  |

|------|---------------------------------------------------------|

| 4.1  | 1 Introduction                                          |

| 4.5  | 2 From Algorithm to Architecture                        |

|      | 4.2.1 Partitioning into Blocks 9                        |

|      | 4.2.2 Exploiting Algorithmic Parallelism 90             |

| 4.3  | 3 The Target Hardware                                   |

| 4.4  | 4 Hardware Architecture                                 |

|      | 4.4.1 System Framework                                  |

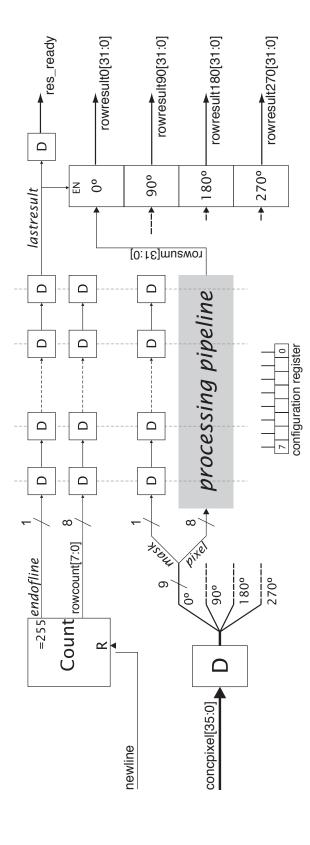

|      | 4.4.2 Top Level Control                                 |

|      | 4.4.3 Rotation Block                                    |

|      | 4.4.4 Functional Blocks                                 |

|      | 4.4.5 Aggregator                                        |

| 4.   | 5 Platform Considerations                               |

| 4.0  | 5 Implementation Results                                |

| 4.   | 7 Summary                                               |

| 5 Fl | exible Functional Blocks for Exploration 120            |

| 5.   | 1 Introduction                                          |

| 5.2  | 2 A Framework for Designing Flexible Functionals        |

|      |                                                         |

|      | 5.2.1 Integration into Trace Transform Architecture 125 |

|   | 5.3                              | Initially Proposed Functionals                                                                                                                                                                                                                                                 |  |

|---|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | 5.4                              | Flexible Functional Blocks                                                                                                                                                                                                                                                     |  |

|   |                                  | 5.4.1 Type A Functional Block                                                                                                                                                                                                                                                  |  |

|   |                                  | 5.4.2 Type B Functional Block                                                                                                                                                                                                                                                  |  |

|   |                                  | 5.4.3 Type C Functional Block                                                                                                                                                                                                                                                  |  |

|   |                                  | 5.4.4 Functional Coverage                                                                                                                                                                                                                                                      |  |

|   |                                  | 5.4.5 Accuracy Considerations                                                                                                                                                                                                                                                  |  |

|   | 5.5                              | Initialisation                                                                                                                                                                                                                                                                 |  |

|   | 5.6                              | Performance and Area Results                                                                                                                                                                                                                                                   |  |

|   | 5.7                              | Summary                                                                                                                                                                                                                                                                        |  |

|   |                                  |                                                                                                                                                                                                                                                                                |  |

| 6 | Lar                              | ge-Windowed, One-Dimensional Median and Weighted Me-                                                                                                                                                                                                                           |  |

| 6 |                                  | ge-Windowed, One-Dimensional Median and Weighted Men Filters 150                                                                                                                                                                                                               |  |

| 6 |                                  |                                                                                                                                                                                                                                                                                |  |

| 6 | diaı                             | n Filters 150                                                                                                                                                                                                                                                                  |  |

| 6 | diai                             | n Filters       150         Introduction                                                                                                                                                                                                                                       |  |

| 6 | dia:<br>6.1<br>6.2               | Introduction                                                                                                                                                                                                                                                                   |  |

| 6 | dian<br>6.1<br>6.2<br>6.3        | In Filters       150         Introduction       150         Definition       152         Related Work       154         Proposed Architecture       157         6.4.1 General Overview       157         6.4.2 Sliding Window Implementation       161                         |  |

| 6 | dian<br>6.1<br>6.2<br>6.3<br>6.4 | Introduction       150         Definition       152         Related Work       154         Proposed Architecture       157         6.4.1 General Overview       157         6.4.2 Sliding Window Implementation       161         6.4.3 Extension to Weighted Median       164 |  |

| 7 Ha | dware Acceleration of Pseudo 2-Dimensional Hidden M | arkov |

|------|-----------------------------------------------------|-------|

|      | del Decoding                                        | 181   |

| 7.1  | Introduction                                        | 181   |

| 7.2  | The Hidden Markov Model                             | 185   |

|      | 7.2.1 2-Dimensional Representation                  | 18!   |

|      | 7.2.2 System Overview                               | 180   |

| 7.3  | Computational Considerations                        | 18'   |

|      | 7.3.1 Log Domain Representation                     | 18    |

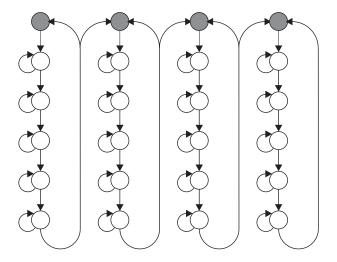

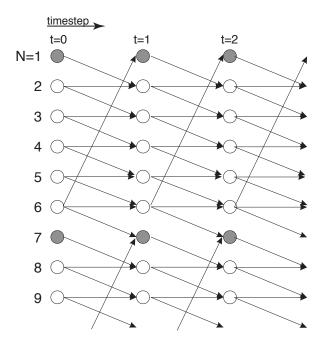

|      | 7.3.2 Trellis Structure                             | 189   |

|      | 7.3.3 Algorithmic Parallelism                       | 19    |

| 7.4  | Proposed Architecture                               | 19    |

|      | 7.4.1 Implementation Considerations                 | 198   |

|      | 7.4.2 Dataflow considerations                       | 19    |

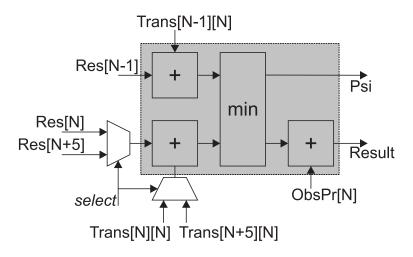

|      | 7.4.3 Single-node Implementation                    | 19    |

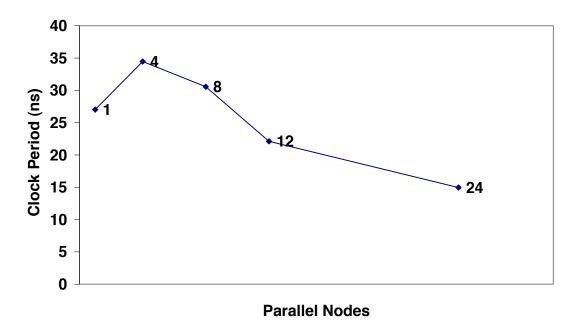

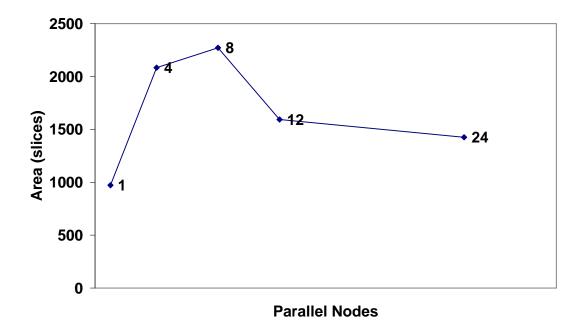

|      | 7.4.4 Multi-node Implementations                    | 190   |

| 7.5  | Implementation Results                              | 19'   |

| 7.6  | Extension to the General Case                       | 199   |

| 7.7  | Summary                                             | 20    |

| 8.2 | Future | Work . |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 205 |

|-----|--------|--------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

# List of Figures

| 1.1 | A typical computer vision processing flow                                 | 18 |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | A vision flow incorporating the work in this thesis                       | 21 |

| 2.1 | VHDL Code                                                                 | 43 |

| 2.2 | Handel-C Code                                                             | 43 |

| 2.3 | Circuit corresponding to the VHDL and Handel-C descriptions               |    |

|     | in Figures 2.1 and 2.2                                                    | 43 |

| 2.4 | Simple colour to greyscale conversion circuit using only adders           | 51 |

| 2.5 | The system architecture for the face detection and lip extraction         |    |

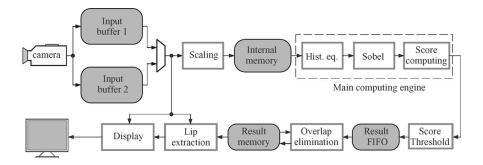

|     | implementation in [NHAS06]                                                | 61 |

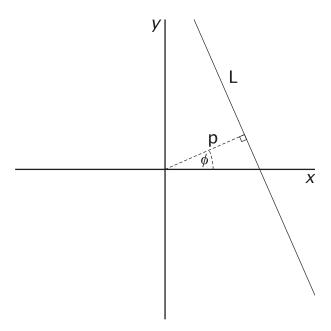

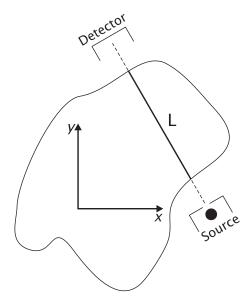

| 3.1 | Coordinates describing a line $L$                                         | 65 |

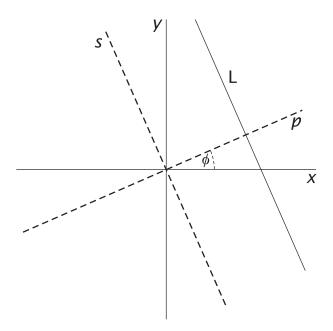

| 3.2 | Coordinates describing a line ${\cal L}$ relative to original and rotated |    |

|     | coordinates                                                               | 66 |

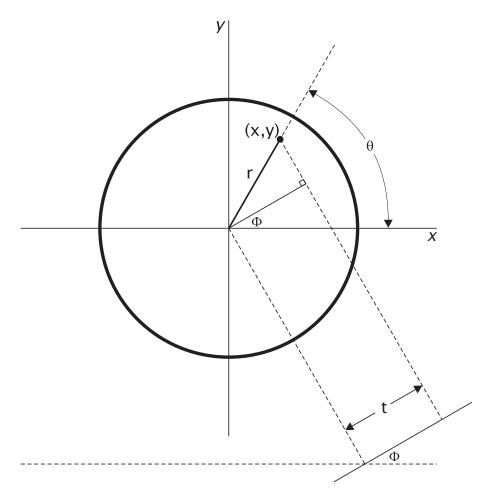

| 3.3 | Geometry for obtaining the $\phi$ -backprojection                         | 69 |

| 3.4 | A beam passes through the region of interest                              | 70 |

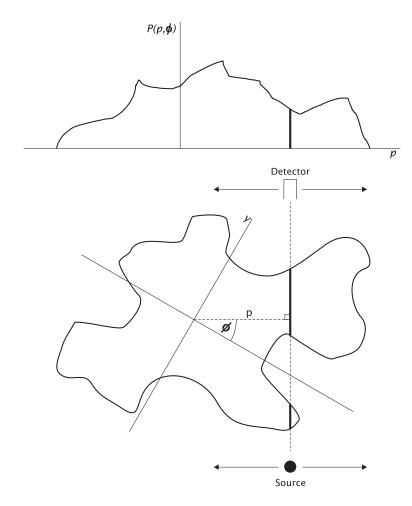

| 3.5  | For a fixed angle $\phi$ , the source and detector move (varying $p$ )   |

|------|--------------------------------------------------------------------------|

|      | and this creates a profile, $P(p,\phi)$ for angle $\phi$ . (Adapted from |

|      | [Dea83])                                                                 |

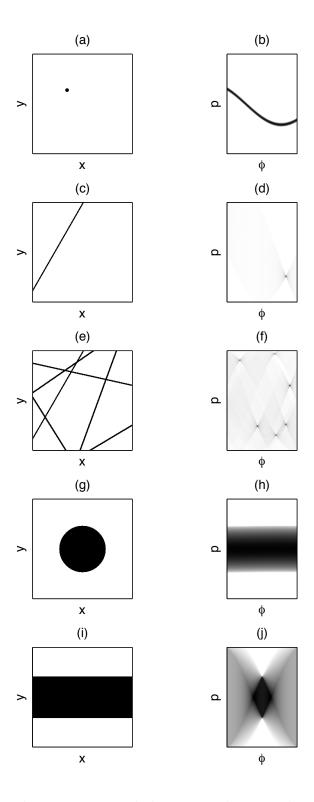

| 3.6  | Some basic images and their equivalents in the Radon parameter           |

|      | domain                                                                   |

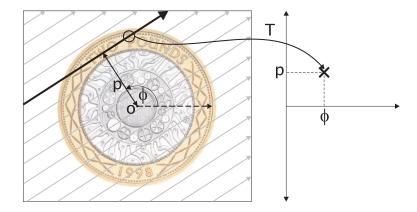

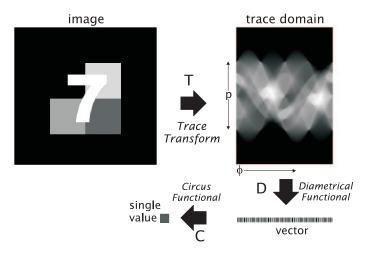

| 3.7  | Mapping of an image to the Trace parameter domain                        |

| 3.8  | An image, its trace, and the subsequent steps of triple feature          |

|      | extraction                                                               |

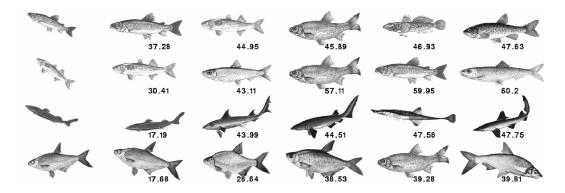

| 3.9  | Examples of queries to the image database and the first five             |

|      | matches returned for each [KP01]. © 2001 IEEE 79                         |

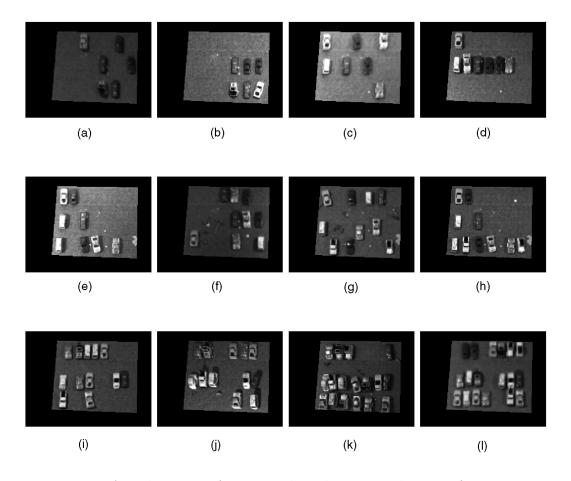

| 3.10 | Aerial images of a car park with varying degrees of activity. $$ . $$ 82 |

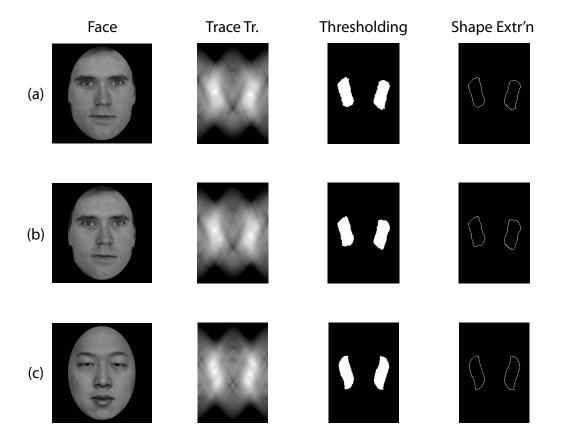

| 3.11 | The Shape Trace Transform for face authentication 85                     |

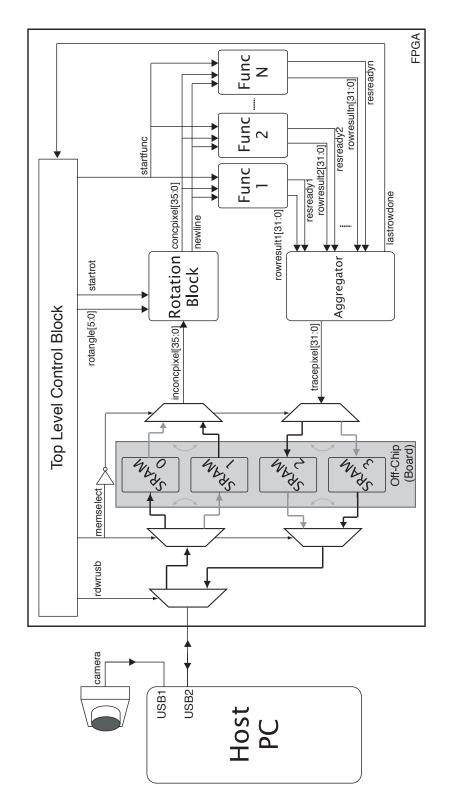

| 4.1  | Trace Transform Hardware Architecture Overview 99                        |

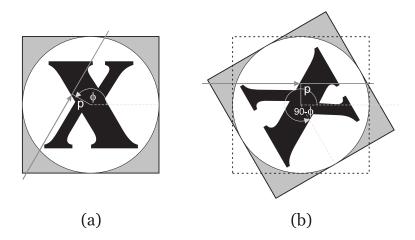

| 4.2  | Image rotation as an alternative to line extraction                      |

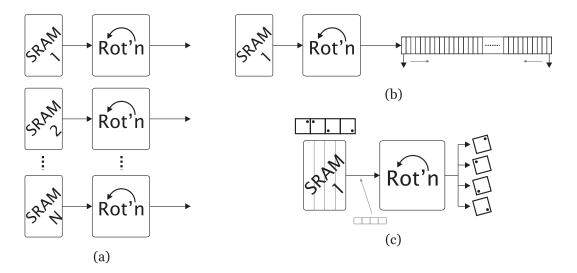

| 4.3  | Three methods for parallelising rotations                                |

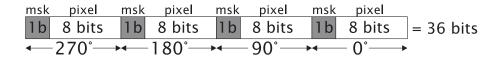

| 4.4  | Structure of a single word in external RAM                               |

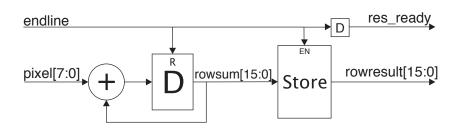

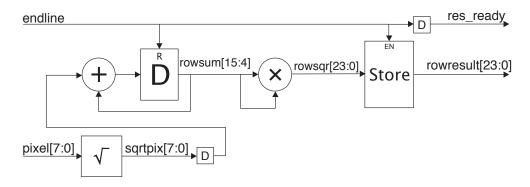

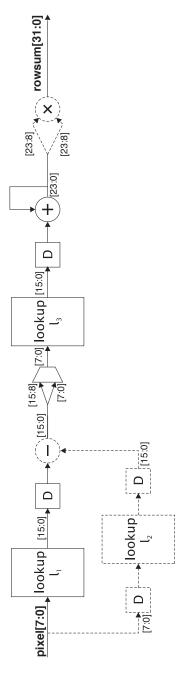

| 4.5  | Schematic diagram of Functional 1                                        |

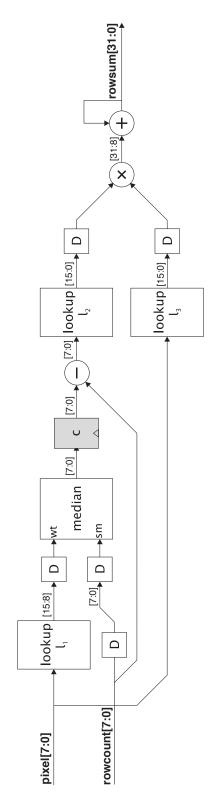

| 4.6  | Schematic diagram of Functional 2                                        |

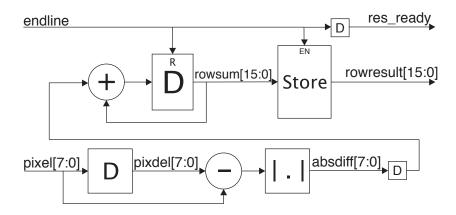

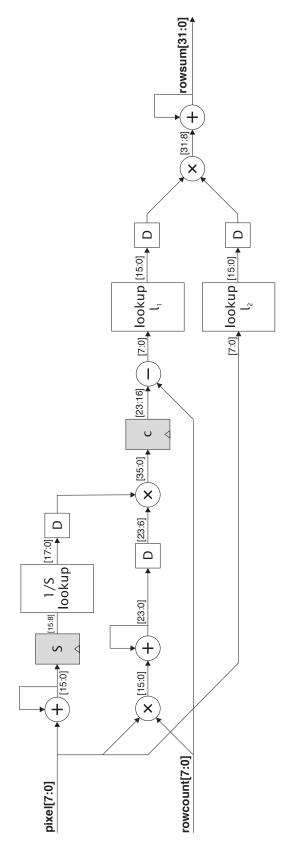

| 4.7  | Schematic diagram of Functional 3                                        |

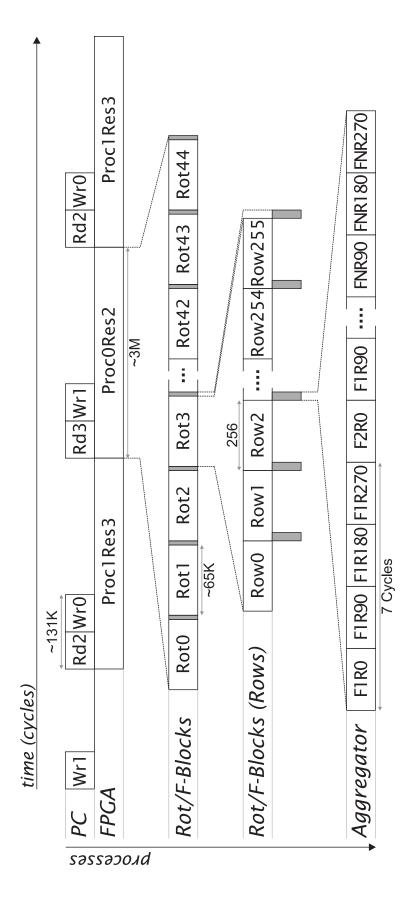

| 4.8  | System-level timing of the Trace transform architecture 117              |

| 5.1  | Flexible functional block framework                                      |

| 5.2  | Type A functional block dataflow diagram                                 |

| 5.3  | Type B functional block dataflow diagram                          |

|------|-------------------------------------------------------------------|

| 5.4  | Type C functional block dataflow diagram                          |

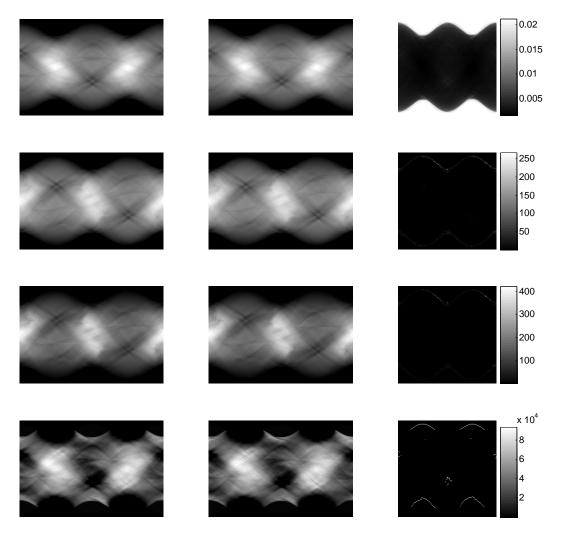

| 5.5  | Trace images obtained using floating point arithmetic (left), the |

|      | equivalents using the hardware architecture (centre), and error   |

|      | images with percentage range (right)                              |

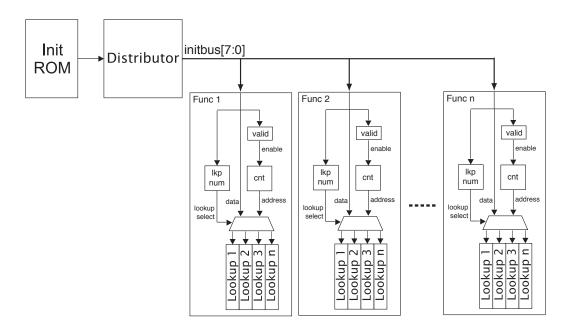

| 5.6  | Flexible functional initialisation bus                            |

| 5.7  | Functional lookup initialisation data format, as stored in the    |

|      | board RAM                                                         |

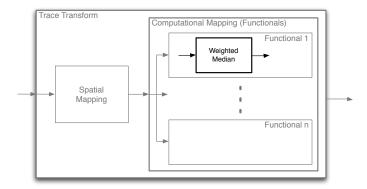

| 6.1  | Position of median and weighted median circuit within a Trace     |

|      | transform implementation                                          |

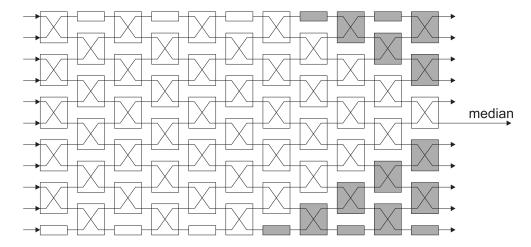

| 6.2  | A simple 11-sample bubble-sorting circuit layout                  |

| 6.3  | A histogram bin node processor                                    |

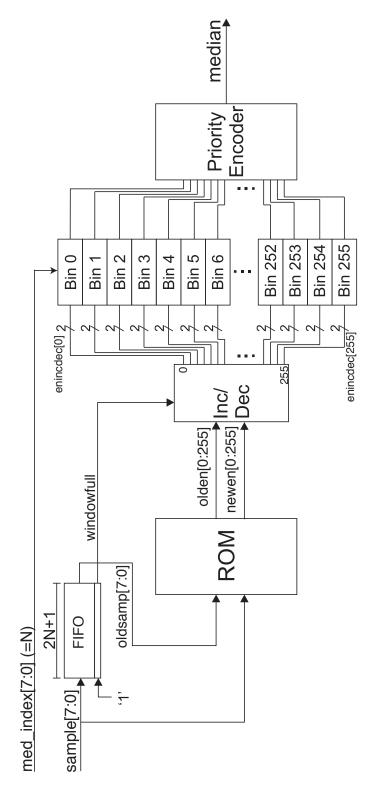

| 6.4  | Histogram-based median filter architecture                        |

| 6.5  | A bin node for the sliding window implementation                  |

| 6.6  | Application to sliding windows                                    |

| 6.7  | Architecture of the sliding window median filter                  |

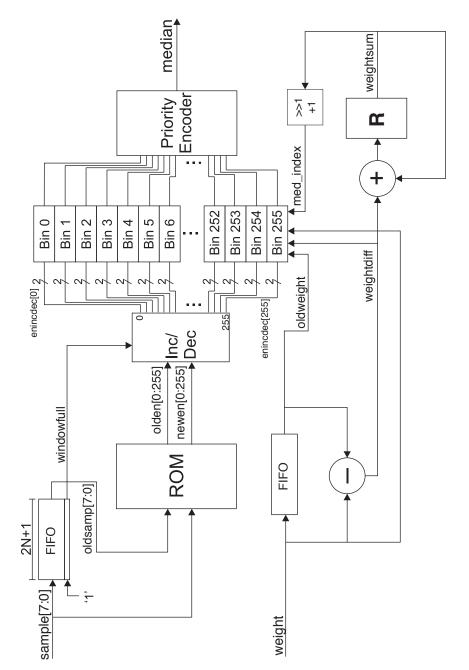

| 6.8  | Architecture of the weighted median filter                        |

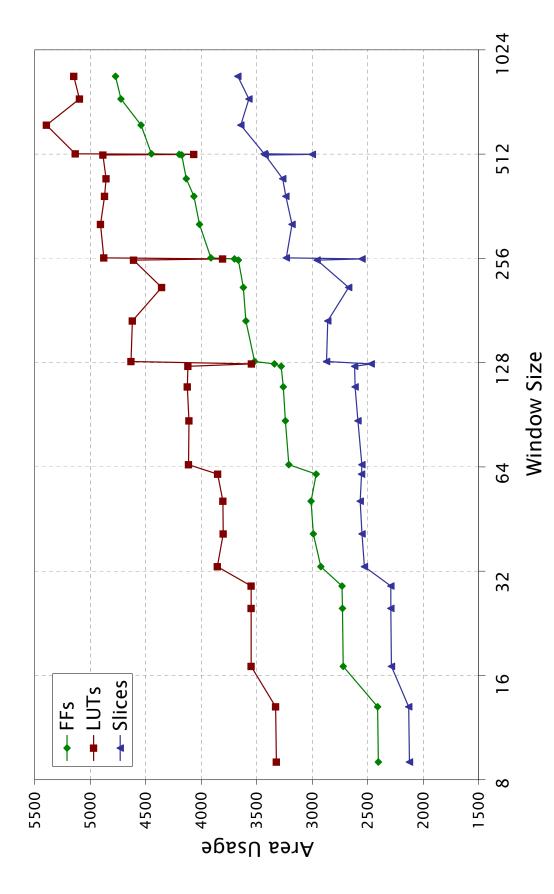

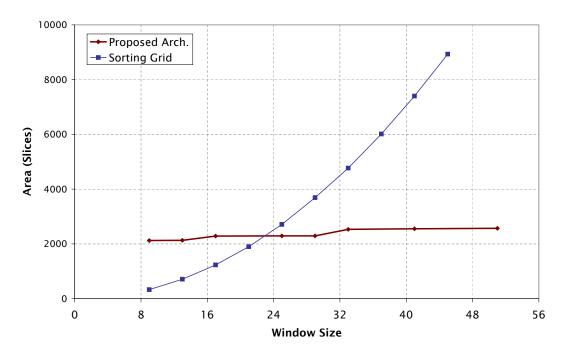

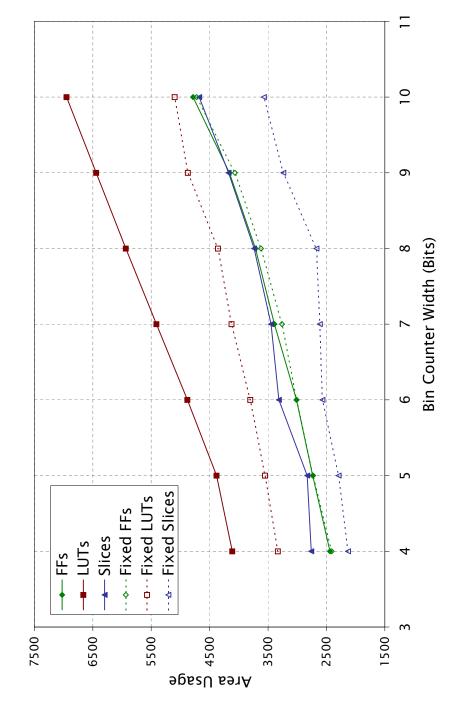

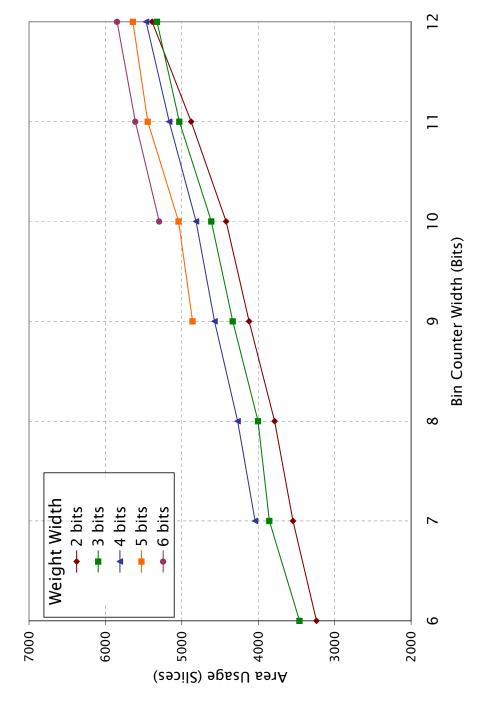

| 6.9  | Graph of synthesis results for various window sizes               |

| 6.10 | Comparison of area requirements for proposed algorithm and        |

|      | sorting grid                                                      |

| 6.11 | Comparison of area requirements for fixed value and variable      |

|      | comparators                                                       |

| 6.12 | Area requirements for various weight and bin width combinations.177    |

|------|------------------------------------------------------------------------|

| 7.1  | State representation of the pseudo 2-dimensional HMM 186               |

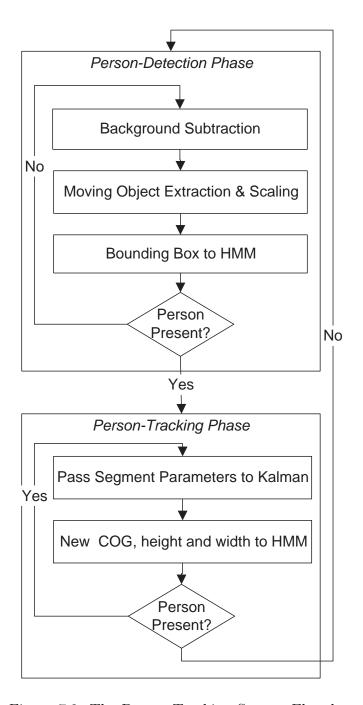

| 7.2  | The Person-Tracking System Flowchart                                   |

| 7.3  | Extract from the state-transition trellis for the pseudo 2-dimensional |

|      | Hidden Markov Model                                                    |

| 7.4  | The efficient HMM decoder node design                                  |

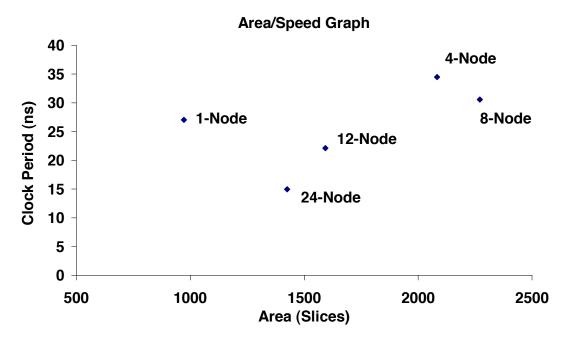

| 7.5  | Impact of number of nodes on clock period                              |

| 7.6  | Impact of number of nodes on area                                      |

| 7.7  | Plot of area and clock period for different numbers of nodes           |

|      | implemented                                                            |

# List of Tables

| 2.1 | Advantages and disadvantages of various target platforms 33         |

|-----|---------------------------------------------------------------------|

| 3.1 | Trace transform computational parameters                            |

| 4.1 | Base orthogonal rotation coordinates, for an $N \times N$ image 106 |

| 4.2 | Trace Functionals                                                   |

| 4.3 | Trace transform architecture synthesis results for the Celoxica     |

|     | RC300 Development Board                                             |

| 5.1 | Mean relative error of functions when approximated by a 256×16      |

|     | bit lookup memory (using maximum possible lossless scaling).        |

|     | x ranges from 0 to 255                                              |

| 5.2 | The Trace Functionals $T$ used in [SPKK05], grouped by simi-        |

|     | larly structured sets                                               |

| 5.3 | Configuration register for Type A functional block                  |

| 5.4 | Type A functional configurations                                    |

| 5.5 | Type B functional configurations                                    |

| 5.6 | Type C functional configurations                                    |

| 5.7 | Synthesis Results for the Three Flexible Functional Blocks 145 |

|-----|----------------------------------------------------------------|

| 5.8 | Running Times and Speedup                                      |

| 6.1 | Access pattern ROM contents                                    |

| 6.2 | Extra sliding window logic                                     |

| 7.1 | Implementation Results                                         |

# Chapter 1

## Introduction

Humans interact daily with their surroundings, through perception via our senses and physical interaction with our limbs. When a sensing faculty is disabled, or its ability diminished, one's perception of his surroundings decreases, and so he acts with more uncertainty. As humans, we are able to process the boundless information that we receive, especially visually, to build some understanding of the world around us. Images in their pixels and bits serve no specific purpose. It is only through extracting higher-level information that some understanding of the scene in question can be gained.

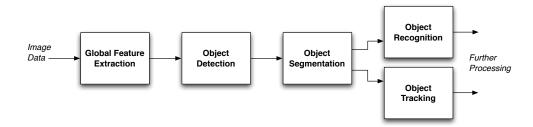

A typical computer vision processing flow is shown in Figure 1.1. Image data is first processed in order to extract features that can be used to represent the image; perhaps edges, corners or other features. These can then be processed to detect the presence of an object. A detected object can be segmented; effectively "cutting it out" of the scene. This object might then be processed for authentication purposes or for temporal tracking or other

Figure 1.1: A typical computer vision processing flow.

higher-order tasks.

Computer vision applications are often characterised by the large amounts of data and processing needed to implement them. The most effective algorithms have often also proven to be some of the most complex. Such algorithms often fail to achieve real-time performance in software and so must be accelerated somehow in order for them to be of significant use. Designing efficient hardware implementations can often propel these systems to the realms of real-time performance. Hardware design is a complex process, and historically, it has been out of the reach of most. This has, however, begun to change recently.

Field Programmable Gate Arrays (FPGAs) are an emerging force in the hardware arena, offering some of the power of custom-designed hardware for a fraction of the effort and cost. Their relative ease of design, low starting cost, rapid time to market and re-configurability make them both an excellent prototyping platform and an ideal alternative to Application Specific Integrated Circuits (ASICs) for medium volume applications. The most significant benefits in any hardware implementation are gained when hardware is designed with the target platform in mind. Modern heterogeneous FPGAs offer a wide

array of resource types which can be exploited in numerous ways. The skill of the designer in exploiting the available resources to their potential is what separates a mediocre system from an efficient, significantly accelerated architecture.

Such a platform provides all the ingredients needed for computer vision research and implementation. FPGAs afford the designer the opportunity to research different algorithms, to incrementally improve implementations and to test applications in the field without huge start-up costs and the associated risks.

The Trace transform is a recently introduced algorithm that has shown to perform well in a variety of image recognition and categorisation tasks. It maps a standard image to an alternative domain, and while defining the spatial mapping, is general in terms of the mathematical aspect. This allows the transform the flexibility to adapt to different applications and for the mathematical components to be selected with respect to their performance for a specific task. The Trace transform is, however, computationally intensive, and acceleration would enable real-time performance that is as yet unachieved in software.

This thesis will investigate the use of FPGAs in computer vision, with the primary focus being the hardware acceleration of the novel Trace transform. All aspects of the implementations will be discussed from design methods, through architectural considerations, down to the implementation results. Beside real-time acceleration, the architecture will be extended to allow for a

fully flexible set of mathematical units, as well as a framework for creating such units and reconfiguring them at runtime. All the architectures presented emphasise the need for considered design and the exploitation of heterogeneous resources to achieve optimum performance.

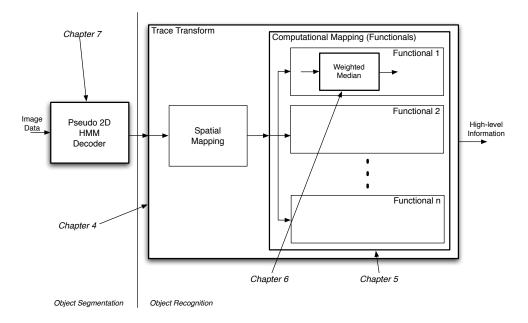

In a vision flow, the Trace transform can be used in numerous ways. It is possible to use the Trace transform to extract global features from an image. These features can be used to characterise certain aspects of the image. An example is the car park usage classification system discussed in Section 3.5.3. The Trace transform has thus far been primarily used for object recognition or authentication, which would typically follow an object segmentation step. The Trace Transform has been applied to image database search [KP01] and face authentication [SPKK05], covered in more detail in Sections 3.5.1 and 3.5.4, respectively.

One of the Trace transform's strengths is its flexibility in terms of the computational mapping. This flexibility is essential in optimally applying the transform to a desired application. Hence, this thesis details an architecture that maintains flexibility and scalability. One of the oft-used mathematical functions within these arithmetic blocks is the median and weighted median. Developing an efficient architecture to implement this enables the use of some of the more complex arithmetic mappings.

Pseudo 2-dimensional HMM decoding is a method that is useful in detection and recognition tasks. The work in this thesis is related to an application used for person tracking [BR03]. Similar systems have been used for face

Figure 1.2: A vision flow incorporating the work in this thesis.

detection [Nef99]. The pseudo 2-dimensional HMM can be used as a stage prior to the Trace transform, that extracts an object of interest for processing by the transform.

An overview of a vision flow incorporating the work in this thesis is shown in Figure 1.2.

#### 1.1 Thesis Outline

The remainder of this thesis is composed of seven further chapters as follows:

Chapter 2 covers general background information on Field-Programmable Gate Arrays, the architectures, design processes and performance metrics used to measure implementations. A general overview of the Computer Vision domain is given with a summary of FPGA implementations of various algorithms.

Chapter 3 is an introduction to the Trace transform and its precursor, the Radon transform. The mathematical foundations of the Radon transform are introduced, followed by a brief overview of its applications. The Trace transform is then defined before looking at a variety of applications and discussing its different modes of use. Finally, some analysis of its computational complexity is presented.

In Chapter 4, a hardware architecture is developed for the Trace transform that provides for real-time acceleration of the algorithm. The architecture is detailed showing how significant acceleration is achieved through the exploitation of algorithmic parallelism. The architecture presented is extensible, and can be used to build up a full recognition system using the Trace transform.

In Chapter 5, a framework for developing flexible, re-programmable functionals is presented. The framework interfaces with the architecture developed in Chapter 4, and while adding significant flexibility, has no adverse impact on performance. As a reference, three flexible functional blocks are implemented, each with the capability to compute a number of different functionals from an existent implementation. The framework facilitates the exploration of Trace transform functionals for a given application.

In Chapter 6, a highly efficient hardware implementation of large-windowed median and weighted median filters is developed. This implementation assists in implementing some of the more complex Trace transform functionals in a real-time system. Numerous design variations including fixed vs. sliding windowed, fixed vs. variable median index, standard vs. weighted median are

investigated in terms of their area usage.

In Chapter 7, a hardware architecture for Hidden Markov Model (HMM) decoding for person detection is presented. Such a system can serve as an initial step in a full person recognition system, extracting frames of interest from a video stream which can then be processed using the Trace transform. The HMM decoding is accelerated by analysing the state transitions and optimising the hardware accordingly, while also exploiting algorithmic parallelism. The architecture is generalisable to any pseudo-2D HMM.

Finally, in Chapter 8, the work is summarised, along with the conclusions reached from these implementations. Finally, some suggestions for future work are given.

#### 1.2 Contributions

The main contributions of this thesis are as follows:

- A thorough computational analysis of the Trace transform, including a look at areas of algorithmic parallelism that can be exploited for hardware acceleration. (Section 3.6).

- The first hardware implementation of an extensible Trace transform architecture, which achieves real-time processing speeds, while remaining fully flexible in terms of the number of functionals implemented. A novel approach to parallelising rotations through the concatenation of orthogonal base rotations quadruples performance while designing the

architecture to process a stream of image data removes the need for any internal buffering. (Chapter 4).

- A framework for developing flexible functionals for use in the Trace transform architecture mentioned above, including three examples. Embedded memories on the FPGA are used for function evaluation, and multiple datapaths are selectable via a configuration register, thus allowing a single functional block to compute a range of different functional equations. This framework serves as an ideal platform for further investigation of the Trace transform itself for a variety of applications. (Chapter 5).

- A highly flexible set of architectures for implementing one-dimensional large-windowed median and weighted median filters for image processing. A rank of cumulative histogram bins is addressed in parallel, keeping a fully updated cumulative histogram with every sample that enters the system. The architecture is unique in its ability to process windows of arbitrary size, and without an area increase. The architecture implements both standard and weighted median calculation for fixed and variable windows. (Chapter 6).

- A real-time acceleration of Pseudo 2-dimensional Hidden Markov Model decoding. By considering the state transition trellis for a pseudo 2dimensional HMM, significant simplifications can be made to the decoding stage. This simplifies the otherwise complex Viterbi calculation used in the system. The pseudo 2D HMM has been shown to be applicable to

image segmentation as part of an object tracking system. (Chapter 7).

#### 1.3 Publications

Parts of the work detailed in this thesis have also been separately published in the following publications:

- "Hardware Acceleration of Hidden Markov Model Decoding for Person Detection" S.A. Fahmy, P.Y.K. Cheung, W. Luk. Proceedings of Design, Automation and Test in Europe (DATE), 7-11 March 2005, Munich, Germany. Volume 3, Pages 8-13. [FCL05a]

- "Novel FPGA-Based Implementation of Median and Weighted Median Filters for Image Processing" S.A. Fahmy, P.Y.K. Cheung, W. Luk. Proceedings of International Conference on Field Programmable Logic and Applications (FPL), 24-28 August 2005, Tampere, Finland. Pages 142-147. [FCL05b]

- [FBCL06]: "Efficient Realtime Implementation of the Trace Transform"

S.A. Fahmy, C.-S. Bouganis, P.Y.K. Cheung, W. Luk. Proceedings of International Conference on Field Programmable Logic and Applications (FPL), August 2006, Madrid, Spain. [FBCL06]

- "Real-Time Hardware Acceleration of the Trace Transform" S.A. Fahmy,

C.-S. Bouganis, P.Y.K. Cheung, W. Luk. Journal of Real-Time Image

Processing: Special Issue on Field-Programmable Technology, Springer,

December 2007. [FBCL07]

• "From Algorithms to Architecture" S.A. Fahmy, C.-S. Bouganis, P.Y.K. Cheung. Chapter 11 of A. Bharath and M. Petrou (editors) Reverse Engineering the Human Vision System, Artech Publishers, to appear in 2008. [BM08]

# Chapter 2

# Background

#### 2.1 Introduction

Field Programmable Gate Arrays (FPGAs) are a relatively recent development when considered against the backdrop of decades of development in the field of digital electronics. The simple digital circuits of yesteryear were often constructed using off-the shelf logic devices that could manage only a very primitive, single logic operation each. A board with hundreds of these small chips might implement an archaic system of minimal complexity. Only the most well-funded corporations could afford to design their own devices from the ground up, using what were the cutting edge Computer-Aided Design (CAD) tools of their time, and the newly emerging integrated circuit (IC) technologies. For the hobbyist or small company or research effort, these "advanced" technologies were out of reach.

The emergence of ICs, driven initially by some high-profile aerospace projects

saw the start of a rapidly developing landscape of custom designed integrated circuits, offering high performance and compactness. The growth has been exponential, and today, some Application Specific Integrated Circuits (ASICs) contain hundreds of millions of transistors on-die.

In this chapter, background information on FPGAs will be provided, with some insight into the design process and various design decisions that must be made.

A review of some hardware implementations of computer vision applications will also be presented. Computer vision systems are computationally very complex, and hardware implementations are often required for real-time performance. Background related to the Trace transform will be presented in the next chapter.

#### 2.2 Field Programmable Gate Arrays

Field Programmable Gate Arrays (FPGAs) were invented in 1984 by Ross Freeman [Xil04], one of the founders of Xilinx Inc. In 1985, Xilinx released their first FPGA, the XC2064 which contained 64 logic blocks and 1000 gates [Xil04]. Today, FPGAs have become a viable platform for implementing some of the most complex digital designs with sizes the equivalent of tens of millions of gates. Whereas FPGAs were seen as a platform for implementing glue-logic in the early days, they now find use in a wide range of applications, and often feature in end-market products.

When choosing an implementation platform for a given application or product, the typical choice one would make is between custom ASIC, some form of Application-Specific Standard Platform (ASSP), such as Digital Signal Processors (DSPs) or Graphics Processing Units (GPUs) and standard General Purpose Processors (GPPs). GPPs are simpler versions of what one might find in his PC; simple microprocessors that can compute a wide variety of different functions by breaking them up into standard instructions that are manageable by the on-die resources. Typically, an application would be programmed in a familiar high-level language and a compiler would then translate this into native "machine-code". ASSPs are processors suited to a specific implementation domain; typically the on-die pipelines and processing units are tailored to the needs of specific tasks required by the target domain. DSPs (e.g. Texas Instruments TMS320 series) are the most prevalent and typically allow for real-time implementation of complex signal processing applications. GPUs (e.g. ATI Radeon series) are highly optimised for graphics tasks, and indeed the transistor count of some GPUs exceeds that of many top-end GPPs. Network processors are another form of ASSP that has become widely used in the field of networking. ASSPs are also typically programmed using high-level languages, sometimes with extensions specific to the application domain.

There is little doubt that for the highest possible performance for a given, fixed application, that custom ASICs are the platform of choice. A custom ASIC is designed from the ground up to implement the specified application. A hardware architecture tailored to the system at hand is developed and every-

thing is tweaked to the parameters of the application. The significant speedup results from two things:

Firstly, within most complex algorithms, there is some complex arithmetic computation. When such computations are run on general purpose processors, the steps must be broken down into small instructions that can be executed by the pipeline present on the target device. Standard programming languages make this easier by allowing a coder to specify complex instructions, while the compiler breaks these up into "machine code". Typically, a general purpose processor will have a core processing unit that is capable of computing a fixed variation of simple operations at very high speed. While the number of computations per second may be very high, the number of complete operations per second is significantly reduced. This is especially pronounced when the operations being performed are far from those intended by the design of the pipeline. This is what has pushed the development of ASSPs.

When designing a hardware system, the designer is freed from these constraints, since the computational unit can be tailored to specified requirements, and the designer is free to implement any number of different units. By implementing a core that is custom-designed to implement specific operations, the core can run slower (in terms of clock speed) than a general purpose processor but still have significantly greater processing throughput<sup>1</sup>.

Secondly, an algorithm can be accelerated in hardware through parallel

<sup>&</sup>lt;sup>1</sup>Throughput refers to the real overall processing speed of a system, and is typically measured in full data units completed per second. For image and video processing, the typical measure would be the number of frames processed per second.

computation. Complex algorithms typically iterate over various values of parameters in order to compute one complete result. As an example, a 2-dimensional image filtering algorithm would require iterations along all pixels in the x and y axes. Often there is somewhere in the algorithm where such a set of iterations occurs. In a hardware system, the designer is free to implement as many computational blocks as the resources will allow, and this means that multiple serial iterations can in fact be processed simultaneously. The only limitation is that the results for each iteration of a variable must be independent of each other: the calculation of results for one iteration should not depend on the results of another. When this is the case, the designer can design the system to exploit this algorithmic parallelism in order to afford significant speedup.

As a result of this custom tailored design, the resultant hardware is optimised for speed, area and power, and significantly outperforms the equivalent software system running on a GPP or ASSP. Of course, there are other factors to be considered which reduce this advantage somewhat. Firstly, the design and verification of a custom ASIC is a complex, time-consuming process. As such, the non-recurring engineering (NRE) costs are significant. Couple this with the initial costs of production, which can exceed \$1 million in the case of some of the newer manufacturing technologies, and the long time-to-market and it is clear that economies of scale play a big part in the viability argument. Furthermore, one may wish to consider the increasing rate at which new standards are being introduced. An ASIC implementation is fixed, and thus any

envisaged changes in the design would either have to be incorporated into the initial architecture, or else, a new chip would have to be produced, with the associated costs.

FPGAs can be seen as a half-way house between custom ASICs and AS-SPs. They offer the significant performance advantage of a custom-designed architecture, with much lower NRE and implementation costs than ASICs; they are available as off-the-shelf products. FPGAs are reconfigurable, which means that an implemented design can be changed or replaced, even after system integration. There is no need for low-level verification of a design, since FPGAs are designed to meet specified constraints for on-chip logic and I/O. Of course, there are still other factors to consider in deciding whether to use FPGAs for a specific application. Firstly, an FPGA implementation is still a hardware design, and hence the required knowledge is arguably more specialised than that needed for software implementations. Furthermore, the cost of FPGAs is higher than ASICs for very large quantities. One of the common examples where an ASIC implementation is more enticing is that of codec chips, such as an MPEG-4 decoder. Given a fixed design that will be used in hundreds of millions of devices, across an array of applications, the cost of an ASIC implementation becomes lower than using FPGAs. FPGAs also typically consume more power than equivalent designs in ASIC, so are generally not favoured in mobile applications.

As technology has improved, however, many of the disadvantages of using

| Platform    | Advantages                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------|

| GPP         | Very simple to program, widely available, can be distributed as standard software.                            |

| ASSP        | Simple to program, tailored to application domain, with excellent performance for the specified applications. |

| FPGA        | High performance, significant flexibility, design effort less than ASIC.                                      |

| Custom ASIC | Best performance available, completely tailored to application.                                               |

Table 2.1: Advantages and disadvantages of various target platforms.

FPGAs have been tackled. While much benefit has been gained from general advancements in fabrication processes, a number of functional improvements have seen the FPGA become a more viable target platform for a plethora of application domains. The latest generations of FPGAs have significantly reduced power requirements, are able to run at higher speeds, support a wider array of I/O standards, and offer significantly more complex on-die units. Couple this with the rising costs of implementing cutting-edge ASICs and the rapid development and deployment of new industry standards, and it is clear that the advantages held by FPGAs in terms of rapid design time, and deployment, with reduced time-to-market make them an attractive alternative to ASICs. Some of the trade-offs in selecting a target platform are summarised in Table 2.1.

#### 2.2.1 Logic and Routing

The principle behind an FPGA is an architecture that can implement any arbitrarily defined function. The FPGA is a pre-fabricated circuit, needing nothing more than a simple configuration to be applied in order for it to func-

tion. For the flexibility to implement any function, two requirements must be met. Firstly, there must be simple, flexible circuit elements that can implement arbitrary logic functions; this is often termed the logic fabric. Secondly, there must be some method of connecting such units up in an arbitrary fashion, the routing fabric. These elements are the core of FPGA architectures.

The logic fabric is typically composed of circuit elements built around small Look-Up Tables (LUTs). These can perform any given logic function with a single output. A 4-input LUT can implement any logic function of four variables with a single output. The output of this LUT is typically connected to an optional flip-flop allowing for synchronous circuits. The routing fabric connects multiple logic elements together through switch-boxes. These are separately programmable to connect arbitrary logic elements together. This flexibility is the key to an FPGA's reprogrammability, as well as its ability to implement any design. Both the contents of the LUTs and the routing switches are reconfigurable.

Of course, this level of flexibility comes as a cost. Whereas in an ASIC design, fixed wires route between circuit elements, in an FPGA, signals must travel through the routing fabric including switches and drive wires which may be longer than are absolutely necessary. This all introduces delay, creating a performance gap between an FPGA and ASIC implementation of the same design. One must also consider the fact that a design is targeted to an FPGA with a specified number of logic-elements: the sizes step-up in stages, and so it is likely that some part of the FPGA's logic fabric will be unused in a design.

Enabling the huge number of possible connections in an FPGA architecture also means that the routing is very abundant, which means that a significant portion of chip area is consumed by non-computational elements.

The earlier FPGA architectures, such as the Xilinx 4000 series [Xil99a] and the Altera FLEX 8000 [Alt01b] consisted solely of the logic elements and routing fabric as described above, as well as I/O blocks for off-chip communication. These architectures developed rapidly, with the addition of carry-chain logic to the the basic elements and other tweaks to the logic fabric to allow for more efficient implementation of common design components. The delay-cost of routing has driven significant changes in the routing fabric too, with more considered (and complex) routing arrangement including hierarchical routing and multiple wire lengths. The most recent FPGA devices have departed from 4-input LUTs to 6-input LUTs (in the case of the Virtex 5 [Xil07b]) and adaptive LUTs and adders (in the case of the Stratix III [Alt07]).

#### 2.2.2 Reconfigurability

FPGAs are SRAM-based devices. The logic and routing are configured at runtime, and upon power-off, this configuration is lost. This is why a production FPGA will typically have a Programmable ROM (PROM) that stores the configuration data sited beside it, so that it can configure when it powers-up. This also means that the system configuration can be changed at any time, and the circuit can be modified. Typically, this might be used to try different variations of a circuit or fix problems that arise in simulation. However,

another possibility is what has been termed dynamic reconfiguration. This is where the FPGA configuration is modified while it is running. Partial reconfiguration is where only a part of the circuit is modified at runtime, perhaps to implement an alternative block within the same architecture. A thorough explanation is given in [Sed06].

Unfortunately, the design flow for a reconfigurable architecture is significantly more complex than that for a static architecture. At present, the designer needs to work at a relatively low level, managing the placement of reconfigurable blocks, in order to allow for partial reconfiguration. This situation is changing but as yet, this field remains the preserve of academic research.

### 2.2.3 Embedded Memories

A significant development to FPGA architectures was the addition of other types of resources such as embedded memories, as in the case of the Xilinx Virtex [Xil99c] and Altera FLEX 10K [Alt01a]. If one considers the logic fabric mentioned above, it is clear that implementing memories of any reasonable size would be highly inefficient in LUTs. Memories are useful in many applications, as buffers, FIFOs and for temporary storage. Small embedded memories negate the need for routing between LUTs, thus increasing the speed, and reducing the area and power consumption of memory accesses. This also saves on the need to use off-chip RAM, and thus the costs associated with I/O. The Xilinx Virtex brought between 8 and 32 4Kbit RAM blocks per device (depending on device size). Later, the Xilinx Virtex II [Xil99b] saw these enlarged to 18Kbits

each as well as increasing in number. The Virtex 4 [Xil07a] maintains the same Block RAM configuration, while the Virtex 5 [Xil07b] increases the capacity to 36kbits each. RAMs can also be combined without the use of extra logic in the Virtex 4 and Virtex 5. Altera, on the other hand, has developed a hierarchical memory architecture for its Stratix [Alt05] series, with three different sizes of RAMs on chip. This suits applications where a few large buffers might be needed, as well as small local coefficient memories.

Embedded memories have significant advantages. A 4-input LUT can only implement a 16x1bit ROM. Thus for any reasonable sized memory, a significant number of Slices and consequently routing resources would be required. As a comparison, a 16k×1bit ROM, implemented in logic on a Xilinx Virtex II would use 559 Slices and could only be clocked at 2/3 the speed of the equivalent implemented in a Block RAM [Smi07]. The Block RAMs on the Xilinx Virtex II can be implemented as single- or dual-port ROMs or RAMs, synchronous or asynchronous FIFOs and also data width converters [Xil99b].

# 2.2.4 Embedded Multipliers and DSP Blocks

The Xilinx Virtex II brought with it embedded multipliers. FPGAs had found a significant following in the DSP community and multipliers are a feature of many DSP designs. Since implementing multipliers using LUTs carries with it all the inefficiency of the routing between LUTs, hard-wired multipliers can free up significant resources for other tasks. The Altera Stratix pushed this idea further by implementing a DSP block, another name for a multiply-

accumulator (MAC). The latest Xilinx Virtex 4 and 5 [Xil07a, Xil07b] have followed suit.

Multipliers find their most obvious use in digital filters. In the Virtex II, the architecture was designed with the Block RAMs beside the multipliers so as to minimise routing delays between the coefficients, typically stored in memories, and the multipliers. Aside from traditional uses, multipliers have also been used as barrel-shifters [Gig04], for implementing floating-point units and even to replace Block RAMs [MCC07]. In fact, multiplications surface in a significant number of image processing applications from colour-space conversion and image rotation, to filtering and image transforms (see [Rus02] for an overview of algorithms). The saving in using embedded multipliers is both in terms of logic fabric and routing resources. An 18×18 bit multiplier implemented in logic on a Xilinx Virtex II would use 201 Slices and would only run at half the speed of the equivalent embedded multiplier [Smi07].

#### 2.2.5 Other Resources

Modern FPGAs include a number of other resources which find uses in various applications. The Xilinx Virtex II Pro introduced embedded PowerPC microprocessors. These are offered on some parts of the new Virtex 4 and 5 families today. Having a processor on chip means that a whole software/hardware solution can be developed on a single chip. This is often termed System-on-a-Programmable-Chip (SoPC) development. The PowerPC can even been used to run an embedded version of Linux on the FPGA [Sai04]. It is also possible to

allow the PowerPC to control runtime reconfiguration of the FPGA [BJRK<sup>+</sup>03]. In those FPGAs where no processor is available, vendors offer a soft processor that can be implemented using the logic fabric. Xilinx offers the MicroBlaze and PicoBlaze, while Altera offers the NIOS processor.

Delay-Locked Loops (DLLs), Phase-Locked Loops (PLLs) and Digital Clock Management (DCM) blocks allow fine control over clock signals, including the facilitation of multiple clock domains in a design. Advanced I/O standards are also supported on some devices, with gigabit transceivers and differential signalling built in to the fabric. I/O is one area where FPGAs shine. Since the I/Os are verified against multiple standards one need not concern themselves with this process, as would be the case with an ASIC design.

## 2.2.6 The FPGA Design Flow

The FPGA design flow is similar to that of standard ASIC hardware, but with some notable differences due to the different target platform. Here, the various steps are detailed along with a discussions of some of the design decisions that can be taken.

## Design Entry

The first step in the flow is design entry. This is where the hardware architecture is specified. This can be done at a number of different levels of abstraction, and using various different tools and languages. One of the more archaic methods is Schematic Capture. Typically a computer-based design

program, that contains visual representations of basic building blocks, is used. The designer places these on a canvas, defines the parameters of each of the blocks then connects them graphically, as required. The designer then defines the inputs to the system and its outputs, and the tools take care of the rest. However, with the increase in design complexity, this method of design entry has become more rarely used.

Another method is the use of Hardware Description Languages (HDLs). These are special languages used to describe hardware. Initially, they were used to describe a circuit structurally, in terms of its low-level components. These languages can also be used to describe hardware at Register Transfer Level (RTL), where the system is designed in terms of a set of registers and transfer functions describing the flow of data between them. Now, a more significant portion of designs are described at a behavioural level. At this level of abstraction, the designer specifies what the circuit does, leaving the synthesis tools to determine how to implement this behaviour. As an example, the designer can simply specify A+B=C, and the compiler will determine the circuitry to do this. This allows the designer to focus less on the small details, and also means that the same code can be used to target multiple architectures using appropriate synthesis tools. The foremost HDLs used today are VHDL and Verilog.

Recently, significant effort has been spent in developing tools that allow the designer to work at higher levels of abstraction. The idea behind "High-Level Synthesis" is that the designer should be free to focus on the system-level design and ignore the details of the hardware implementation. Extensions to the C programming language, such as Handel-C [Cel], add language elements for hardware description yet allow the designer to use familiar C-based syntax. Xilinx's System Generator [Xil] is a tool that latches into Mathworks' Simulink software [Mat], used in DSP design. It allows the hardware designer to draw dataflow graphs to describe a DSP system, and the tools take care of the translation to hardware. High-level synthesis, however, is still relatively novel, and the performance of most tools cannot compete with the performance and compactness of systems designed at lower levels of abstraction. Vendor tools such as System Generator are significantly better than general High-level languages, since often, they contain pre-defined blocks that have already been optimised for hardware implementation. Such tools though, are often restricted to a specific application domain; in the case of System Generator, DSP systems. True general purpose high-level synthesis is much more difficult to achieve, and hence cannot always be considered as the ideal design tool. With languages like Handel-C, the added language constructs still allow the designer to design at a level of abstraction similar to behavioural HDL descriptions, and when used in such a manner, the resultant implementations are significantly faster and more compact than when the language is used in a software-centric way. [CH02] and [TCW<sup>+</sup>05] both discuss the various design tools and descriptions available and the trade-offs associated with high-level synthesis. This, however, remains a fast-developing field and the situation continues to improve. A full scientific study of the trade-offs associated with

different design description would be a welcome resource to assist designers in selecting the most suitable tools.

#### Notes on Handel-C

Since some of the work in this thesis was completed using Handel-C, it is worth noting some of the features of the language and design environment. Handel-C extends a subset of the C language to allow for customisable data widths and parallelism; two essential elements of hardware design. Timing is fixed at one clock cycle per C statement, allowing the designer fine control over circuit scheduling. The compiled circuit is a one-hot state machine that uses token-passing to move from one statement (or a block in the hardware) to the next.

The design environment for Handel-C is the Celoxica DK suite, which provides a code editor and simple simulator. The simulation tools can be awkward for hardware design since concurrency is difficult to track using a variable watch window. The real strength of using the Celoxica tools comes in the board APIs, that enable the use of development board resources with minimal effort, abstracting complex control and data signalling to simple C statements.

Handel-C code is compiled to an EDIF netlist or to VHDL code, that can then be further synthesised, placed and routed using the standard tools described below. Due to the hidden control circuitry, there is an area and speed overhead, but no concrete figures are available, since this depends entirely on the specific application. Massively parallel systems, such as the median

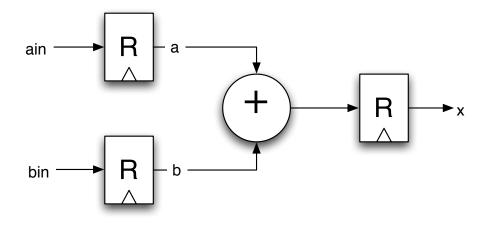

Figure 2.1: VHDL Code

Figure 2.2: Handel-C Code

Figure 2.3: Circuit corresponding to the VHDL and Handel-C descriptions in Figures 2.1 and 2.2.

calculation architecture presented in Chapter 6 suffer more than small regular circuits or those with complex control, but only a few parallel blocks.

Coding in Handel-C can be simpler than VHDl for complex designs. There are numerous constructs that assist in code reuse, and replication. Furthermore, since the clocking is inherent in the code, it can be tidier. Channels allow for timing-blind inter-block communication and synchronisation with ease. Figures 2.1 and 2.2 show a simple block of code in both VHDL and Handel-C (respectively), with the resultant circuit shown in Figure 2.3.

#### **Functional Verification**

In this step of the design flow, the designer confirms that the circuit, as described, implements the desired behaviour. A testbench is written, that wraps the block under test, and feeds it the appropriate data, while monitoring the block's outputs. Tools such as Modeltech's ModelSim [Mod] can be used to analyse waveforms of the outputs as well as signals internal to the block. It is necessary to consider "corner cases", or patterns of data, perhaps unexpected, that could expose some frailty in the system, for example, overflows in arithmetic operations. Once functional verification is complete, the designer's work is for the most part done.

## Synthesis and Mapping

When designing using RTL or behavioural descriptions, these must be translated into primitive hardware blocks. This job is done by the synthesis software, for example Synplicity Synplify Pro [Syn]. An addition specified on a line of code will be turned into an adder. Registers will be created to hold values and the code will be translated into the hardware primitives of the target architecture. When targeting an FPGA, these resources must also be mapped to a type of resource on the device. So portions of logic will be mapped to LUTs and Flip-Flops then clustered into Slices, including the use of carrychains and other resources. As a result, the designer need not be concerned with the granularity of most operations, as the tools will take care of breaking down large blocks into the size required by target hardware. The output of this

stage is a netlist describing hardware resources and the connections between them.

For heterogeneous architectures, the mapping phase is also where decisions are taken as to which type of resource to use. Often, there will be more than one way to implement a hardware block. For example a multiplier could be implemented using standard logic elements or using an embedded multiplier, a FIFO could be implemented using Flip-Flops or embedded memory. Many synthesis tools allow the designer to specify some preference that is taken into account when synthesising. In other cases, the designer must specify the type of resource to use explicitly. There exists a significant body of research that looks at the trade-offs involved in selecting different types of hardware, and the resultant choices that can be made when designing a reconfigurable architecture. [Smi07] contains a good survey of work in the field.

## Placement and Routing

Once the netlist has been produced and the whole circuit has been mapped to the primitives available on the target device, it is necessary to place these instances into specific locations on the device and route the associated signals. The primary aim is to minimise delays by placing communicating blocks adjacent to each other. Once the blocks are placed, it is necessary to configure the routing between them. Again, this is done with the aim of reducing delays. The result of this step is a bitfile, containing all the configuration data needed to set up the circuit in the FPGA device. Typically, in a production system,

this bitfile is stored in a Programmable ROM (PROM), which is accessed by the FPGA on power-up, and used to configure the device.

### **Timing Verification**

After placement and routing, it is necessary to check that specified timing constraints have been met. This is often reported when placement and routing is completed. It is also possible to configure the tools to produce a postplace and route simulation model which can be used to check the resultant circuit using tools like ModelSim. If timing constraints have not been met, the violating paths will be reported, and the designer can attempt to modify those parts of the circuit in order to increase performance.

## 2.2.7 Circuit Measurement Metrics

When designing a circuit, it is necessary to have metrics by which the design can be evaluated. The most obvious metric is that of speed. A faster circuit will process data at a quicker rate. It is important, however to bear in mind that speed should be measured in terms of throughput and not necessarily cycle time. It is possible for a circuit to be clocked at very high speed, but have a relatively low throughput when compared to another circuit with lower clock speed. This is clear when comparing an FPGA implementation against a standard GPP. As shown in Chapter 4 an Intel Pentium 4 Processor running at 2GHz can be outperformed by an FPGA running at 80MHz because the throughput is higher due to parallelism and a more tailored datapath. In

image- and video-processing applications, throughput is usually given in frames per second (fps), though it is important to consider the size of each frame too. In some instances the throughput requirements of a system are fixed, and hence as long as these requirement constraints are met, it is area and power that are of interest.

When discussing the area usage of an FPGA design, the most basic element to be considered is the standard logic element of the target device. In the case of Xilinx FPGAs, area is typically measured in Slices, while for Altera FPGAs, the Adaptive Logic Modules (ALMs) for more recent devices or the Logic Elements (LEs) for older devices, are the measure. Synthesis tools will often report finer levels of resource usage such as flip flops and LUTs, since often the resources can be assigned and packed differently.

With heterogeneous architectures it is also necessary to consider the usage of other resources such as embedded memories and multipliers, since the portions of the circuit mapped to these resources are not represented in the standard Slice count. It is important to note that the proportions of different resources in a device are fixed by the device vendor. As such it may well be possible to deplete the available resources of one type while still having capacity to spare in another type of resource. In such cases, the designer can either target a larger device, or map parts of the circuit from one resource type to another, bearing in mind the performance costs. Memories and multipliers can easily be mapped to use LUTs if needed. Similarly, if some of the standard logic elements are in short supply, the designer should ensure that all portions

of the circuit that can be mapped to other resources are transferred.

Another metric that has more recently gained popularity is that of power. ASIC designers will typically have more control over this, as they can design their architecture to suit. With FPGAs, the power consumption is often out of the hands of the designer, as the static power consumption of the FPGA – which is a subject of the FPGA architecture and manufacturing process – is significant when compared to the dynamic power – caused by circuit switching, and over which the designer may have some influence. In all, FPGAs still consume a significantly greater amount of power than ASICs, at present, and so fail to be considered as an ideal platform for mobile devices. With each transition to newer circuit technologies, the ratio of dynamic power to static power consumption increases, meaning that power considerations will become important to designers in the near future. Currently, the tools provided for power analysis are limited, and techniques for optimising for power obscure. FPGA vendors are pushing forward with architectural solutions such as switching off parts of the chip not in use [TT07]. Development on the two fronts will be necessary in order to assist designers in optimising their designs for power consumption.

When synthesising a design, it is possible to increase the effort level of the tools. This may be necessary when a timing constraint is missed by a small margin, or the design is slightly too large to map to the target device. When the effort is increased, the tools run more aggressive optimisation routines in order to meet constraints. The tools can be instructed to optimise for area or

speed, depending on the requirements of the design.

# 2.3 Hardware Acceleration of Vision Systems

FPGAs provide an ideal platform for prototyping computer vision applications. Such applications are characterised by the large amounts of data processed, and the high computational complexity of the algorithms involved. The provision of heterogeneous resources fairly recently, makes them an even more attractive target platform. Memories specifically can simplify designs hence requiring fewer accesses to external memory, which can often be a bottleneck in a video- or image-processing design. In this section, an overview of some FPGA implementations of vision systems will be presented.

#### 2.3.1 Colour to Black and White Conversion

Images in digital systems are usually represented in the additive three-colour Red-Green-Blue (RGB) domain. However it is often more intuitive to use the HSI (Hue, Saturation, Intensity) colour space. The hue is the colour that is being represented, saturation is how pure the colour is, with full saturation being very strong and zero saturation being grey. Intensity is the brightness of the pixel.

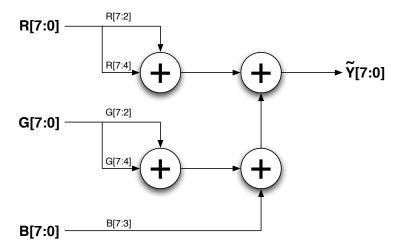

The human vision system is more sensitive to certain wavelengths of light than others, hence in converting from colour to black and white, the colours need to be mixed in different proportions. The standard proportions are shown in (2.1), where Y is the (greyscale) intensity value [Rus02].

$$Y = 0.299 \cdot R + 0.587 \cdot G + 0.114 \cdot B \tag{2.1}$$

For video applications, the input will often be in colour, but most of the complex computation can be performed on the greyscale intensity image to lessen the computational load, then later combined with the colour image if needed. Here, a simple implementation will be presented, to show how for each algorithm, thinking in terms of the target platform is paramount in an efficient implementation. To implement this colour to black and white conversion efficiently, one can recall that in hardware, any base 2 divisions are simply shifts of the bits, or selecting certain bits. Hence, it is possible to come close to the equation mentioned above without having to implement any multipliers. An example is shown in (2.3), where  $\tilde{Y}$  is an approximation of the pixel intensity, given R, G and B input values for red, green and blue respectively. This is much more easily implemented in hardware, with only shifts and 4 two-input adders, as shown in Figure 2.4.

$$\tilde{Y} = 0.3125 \cdot R + 0.5625 \cdot G + 0.125 \cdot B \tag{2.2}$$

$$= \left(\frac{1}{4} + \frac{1}{16}\right) \cdot R + \left(\frac{1}{2} + \frac{1}{16}\right) \cdot G + \left(\frac{1}{8}\right) \cdot B \tag{2.3}$$

Figure 2.4: Simple colour to greyscale conversion circuit using only adders.

## 2.3.2 Object Detection

In object detection, a system must detect the presence of an object of interest in the frame. This can be done in one of two ways. Firstly, it is possible to detect the presence of an arbitrary object. This can only be done with a video sequence, since it is the temporal information that provides the cue that something has been introduced into the scene. Such a form of object detection will often be done using background subtraction, where subsequent frames are extracted from a static reference frame, and areas where there is a difference are treated as objects. Unfortunately, this method requires the camera to be stationary and can be adversely affected by other changes such as illumination. Another method is to use motion vectors to extract moving objects in a video sequence. Areas of the image where the motion vectors close to one another move in the same direction and with the same magnitude are considered as rigid bodies, and can be segmented from the frame. It is important to note that some forms of motion yield different patterns of motion vectors, and depending

on the application, alternative clusterings may have to be considered [YJS06]. With both these approaches, this segmentation gives a bounding box which must then be processed to see whether it is of the type being considered in the system. Simple heuristics such as the consideration that a walking person could only be represented by an object that is taller than it is wide, or that a vehicle may be wider than it is tall, can be used to reject segmented objects without having to process them.

The second type of object segmentation involves analysing the frames with some criteria in mind. Such techniques can depend upon colour, texture, shape or other properties of the image. Often the segmentation can be applied to a single frame, with no need for temporal information. In such a system, objects of interest are often directly segmented from the image.

## 2.3.3 Object Segmentation

Following detection of the presence of an object, it is often necessary to segment this object from the frame. In many cases, detection and segmentation occur together, such as some background subtraction, and most face authentication algorithms. If this is not the case then a number of methods can be employed. Sometimes detection will return the centroid of the desired object, or some other general positional information. In such cases, prior knowledge of the shape of the object can be used to segment it based on these parameters.

Segmentation can also be achieved through the use of edge detection, whether on the image directly, or some property obtained from the detection phase. Edge detection is most often achieved through the use of simple filters like the Sobel or Laplace masks [HS92]. The result of filtering is an edge map where edge pixels have high values and non-edges have close to zero values, or in the case of the Laplace mask, the edges are represented by zero-crossings. Typically, these edges maps correspond to the outline of objects in the scene. Further shape analysis methods can be used to segment the desired objects.

## 2.3.4 Object Tracking

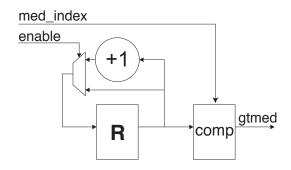

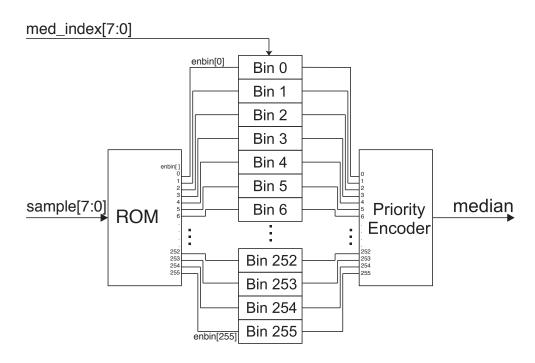

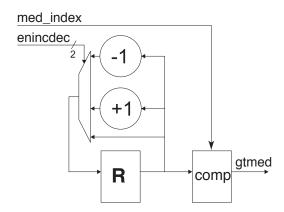

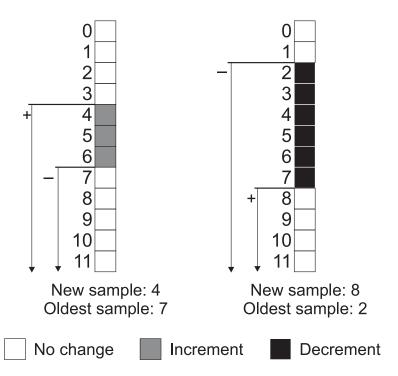

In the case of video sequences, temporal data can be used to track the positions of moving objects in the frame. Numerous methods exist (see [YJS06] for a through survey). Typically, motion vectors will be extracted for a frame. Where a cluster of pixels are determined to have the same motion vectors, a rigid body can be deduced. It is important to note that changes in the background, or camera position introduce many superfluous motion vectors. In some systems, the motion vectors are computed for image features rather than directly on pixel blocks. This reduces the amount of data that needs to be processed.