# EMBEDDED VIRTUALIZATION OF A HYBRID ARM - FPGA COMPUTING PLATFORM

# PHAM DANG KHOA SCHOOL OF COMPUTER ENGINEERING 2014

# EMBEDDED VIRTUALIZATION OF A HYBRID ARM - FPGA COMPUTING PLATFORM

#### PHAM DANG KHOA

School of Computer Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirement for the degree of Master of Engineering

#### **Abstract**

Embedded virtualization is a promising solution for several big challenges in embedded systems, such as ECU consolidation, real-time industrial control, software complexity, safety, security and robustness. However, existing virtualization techniques for embedded systems only consider CPU-based processing solutions. With the trend towards hybrid computing platforms, virtualizing the conventional general purpose microprocessor (the software part) without considering the FPGA (the hardware part) only addresses part of the problem.

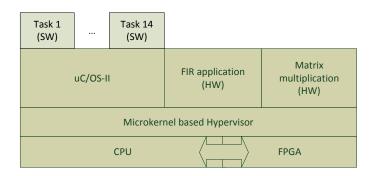

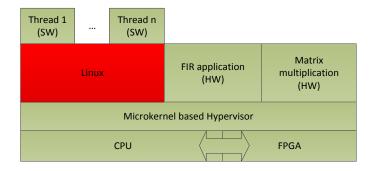

This thesis aims to propose a new approach to embedded virtualization by applying the microkernel-based hypervisor to a hybrid ARM – FPGA platform in order to virtualize both software and hardware tasks. This work involves firstly porting a traditional microkernel-based hypervisor (in this case CODEZERO) to an ARM-based dual core processor on a hybrid computing platform (the Xilinx Zynq 7000). We then examine the necessary modifications to the hypervisor's driver and APIs in order to support the FPGA hardware of the hybrid platform. An integrated hardware accelerator running on the FPGA under hypervisor control is developed as a prototype to evaluate the ability and functionality of the modified hypervisor. In order to compare the performance and hardware utilization of the hypervisor to Embedded Linux, the context switch overhead and the idle time of the hardware module are examined. Experimental results are presented that show CODEZERO is able to switch hardware contexts two to three orders of magnitude faster than that of Embedded Linux.

# Acknowledgement

I would like to express my deep gratitude to Assoc Prof Dr Douglas Leslie Maskell for his patient guidance, enthusiastic support and strong encouragement. His widespread experience and strong technical background helped to clarify my doubts and overcome the hurdles.

I highly appreciate all Asst Prof Dr Suhaib A Fahmy's help, suggestions and recommendations. His deep knowledge in reconfigurable computing is very useful for this project.

I would like to thank my friends Cui Jin and Abhishek Kumar Jain in CHiPES for their support and their help to make me understand the concepts about virtualization, embedded hypervisor and intermediate fabrics. Moreover, they also help me implement some parts of the hardware platform for this project.

I also thank to the TUM CREATE for their partial support for this project.

Finally, I wish to thank my parents and my wife for their support and encouragement during my study.

# **Table of Contents**

| Abstract                                             | 1  |

|------------------------------------------------------|----|

| Acknowledgement                                      | 2  |

| Table of Contents                                    | 3  |

| Table of Figures                                     | 8  |

| Chapter 1 Introduction                               | 12 |

| 1.1 Motivation                                       | 12 |

| 1.2 Contribution                                     | 13 |

| 1.3 Organization                                     | 14 |

| Chapter 2 Background                                 | 15 |

| 2.1 Definitions and concepts                         | 15 |

| 2.1.1 Embedded virtualization                        | 15 |

| 2.1.2 Hypervisor or virtual machine manager          | 15 |

| 2.1.3 Para-virtualization versus full-virtualization | 16 |

| 2.1.4 Microkernel                                    | 17 |

| 2.1.5 Benefits of virtualization on embedded systems | 18 |

| 2.1.6 Constraints for embedded virtualization        | 22 |

| 2.2 Existing virtualization techniques               | 23 |

| 2.3 CODEZERO                                         | 26 |

| 2.3.1     | System partitioning by using containers                        | 27 |

|-----------|----------------------------------------------------------------|----|

| 2.3.2     | Communication by IPC and shared memory                         | 29 |

| 2.3.3     | Virtualization                                                 | 30 |

| 2.4 Sur   | mmary                                                          | 31 |

| Chapter 3 | Porting CODEZERO on ZedBoard                                   | 32 |

| 3.1 Vir   | rtualizing the Xilinx Zynq 7000 extensible processing platform | 32 |

| 3.2 Bo    | oting CODEZERO on the ZedBoard                                 | 35 |

| 3.2.1     | The overall boot sequence                                      | 35 |

| 3.2.2     | CODEZERO's folder structure and final image layout             | 37 |

| 3.2.3     | CODEZERO loader porting                                        | 41 |

| 3.2.4     | CODEZERO kernel initialization porting                         | 42 |

| 3.3 CO    | DDEZERO port detail                                            | 46 |

| 3.3.1     | Zynq 7000 base address definitions                             | 46 |

| 3.3.2     | Rewriting the drivers                                          | 46 |

| 3.3.3     | Enabling the MMU                                               | 49 |

| 3.3.4     | Secondary CPU wake-up and FPGA clock initialization            | 51 |

| 3.4 Sur   | mmary                                                          | 52 |

| Chapter 4 | SW-HW virtualization platform                                  | 53 |

| 4.1 Pla   | ntform framework                                               | 53 |

| 4.1.1     | Overview                                                       | 53 |

| 4.1.2     | The hybrid platform                                            | 54 |

| 4.1.2.1 Task communication                           | 55 |

|------------------------------------------------------|----|

| 4.1.2.2 Context Frame Buffer                         | 56 |

| 4.1.2.3 Context sequencer                            | 56 |

| 4.1.2.4 Reconfigurable Fabric                        | 57 |

| 4.1.2.4.1 Reconfigurable Intermediate Fabric [26]    | 57 |

| 4.1.2.4.2 DPR region                                 | 60 |

| 4.1.3 The hypervisor support                         | 60 |

| 4.2 The hybrid platform hypervisor                   | 60 |

| 4.2.1 Device driver for the IF                       | 61 |

| 4.2.2 API for task communication                     | 61 |

| 4.2.3 Hardware task scheduling and context switching | 62 |

| 4.2.3.1 Non-preemptive hardware context switching    | 62 |

| 4.2.3.2 Pre-emptive hardware context switching       | 63 |

| 4.3 Case study                                       | 64 |

| 4.3.1 Systolic FIR Filter                            | 64 |

| 4.3.2 Matrix Multiplication                          | 65 |

| 4.3.3 Multiple SW-HW tasks on the ZedBoard           | 66 |

| 4.4 Experiment                                       | 67 |

| 4.4.1 Experiment 1                                   | 68 |

| 4.4.1.1 Purpose                                      | 68 |

| 4.4.1.2 Method                                       | 68 |

| 4       | 1.4.1.3 | Results and explanations                             | 70 |

|---------|---------|------------------------------------------------------|----|

| 4.4.    | .2 Ex   | xperiment 2                                          | 71 |

| 4       | 1.4.2.1 | Purpose                                              | 71 |

| 4       | 1.4.2.2 | Method                                               | 72 |

| 4       | 1.4.2.3 | Results and explanations                             | 73 |

| 4.5     | Summa   | ıry                                                  | 74 |

| Chapter | 5 Co    | onclusion and Future Work                            | 75 |

| 5.1     | Conclu  | sion                                                 | 75 |

| 5.2     | Future  | work                                                 | 76 |

| Appendi | ix A C  | CODEZERO on PandaBoard                               | 78 |

| A.1     | Intro   | duction to the PandaBoard                            | 78 |

| A.2     | Com     | piling CODEZERO to the PandaBoard                    | 79 |

| A.3     | COD     | DEZERO's boot sequence                               | 82 |

| A.4     | Bare    | -metal applications on CODEZERO                      | 83 |

| A.4     | l.1 Ho  | ow to configure a bare-metal application on CODEZERO | 83 |

| A.4     | l.2 H€  | ello-world application                               | 84 |

| A.4     | l.3 Ti  | mer, interrupt & context switch:                     | 84 |

| A.5     | GPO     | S (Linux) implementation on CODEZERO                 | 85 |

| A.6     | RTO     | S implementation on CODEZERO                         | 86 |

| A.7     | Mult    | iple applications running on CODEZERO                | 88 |

| A.7     | 7.1 Tv  | wo hello-world applications                          | 89 |

| A.7.2      | Context switch + Linux | 89 |

|------------|------------------------|----|

| A.7.3      | Linux and Android      | 90 |

| A.8        | Summary                | 93 |

| References |                        | 94 |

# **Table of Figures**

| Figure 1. Type 1 (bare-metal) and Type 2 (hosted) hypervisor         | 16 |

|----------------------------------------------------------------------|----|

| Figure 2. Para-virtualized Linux                                     | 17 |

| Figure 3. Monolithic-kernel based OS versus microkernel based OS     | 18 |

| Figure 4. Primary VM + Backup VM                                     | 19 |

| Figure 5. Infotainment VM + Automotive VM                            | 20 |

| Figure 6. General purpose VM + Legacy VM                             | 21 |

| Figure 7. Personal VM + Enterprise VM                                | 21 |

| Figure 8. PikeOS's structure                                         | 24 |

| Figure 9. OKL4's structure                                           | 24 |

| Figure 10. NOVA's structure                                          | 25 |

| Figure 11. CODEZERO's structure [12]                                 | 27 |

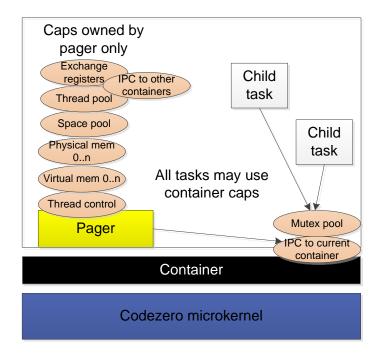

| Figure 12. CODEZERO's containers                                     | 28 |

| Figure 13. Capabilities inside a container                           | 29 |

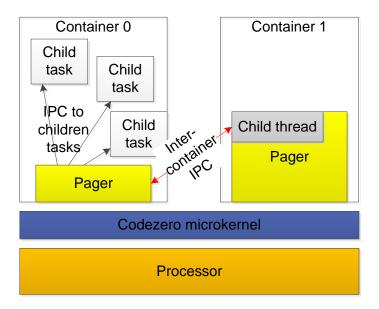

| Figure 14. Inter-process communication inside and between containers | 30 |

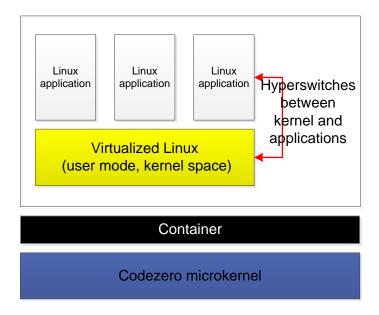

| Figure 15. Para-virtualized Linux on CODEZERO                        | 31 |

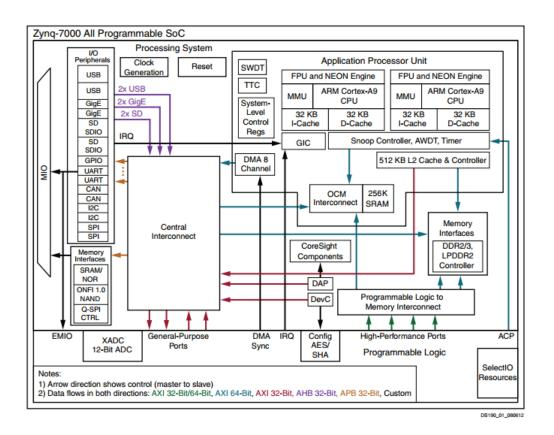

| Figure 16. Zynq 7000's organization [23]                             | 33 |

| Figure 17. Initial idea for SW-HW virtualization platform            | 34 |

| Figure 18. Boot sequence of the ZedBoard                             | 36 |

| Figure 19. The stage 2 boot                                          | 37 |

| Figure 20. CODEZERO's boot sequence                             | 38 |

|-----------------------------------------------------------------|----|

| Figure 21. CODEZERO's shortened folder structure                | 38 |

| Figure 22. CODEZERO final image layout on ZedBoard              | 39 |

| Figure 23. Kernel and Loader start addresses configuration      | 40 |

| Figure 24. Container memory area configuration                  | 40 |

| Figure 25. CODEZERO's detail folder and file structure          | 41 |

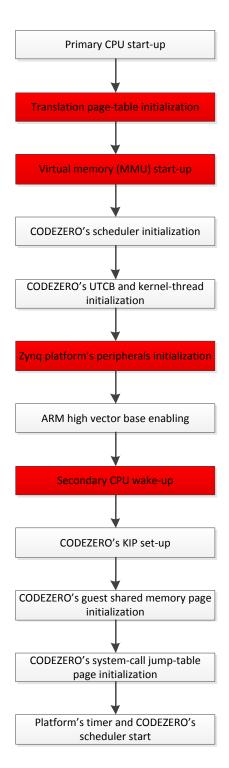

| Figure 26. CODEZERO's platform initialization                   | 45 |

| Figure 27. The UART starts on ZedBoard                          | 48 |

| Figure 28. MMU enable routine                                   | 50 |

| Figure 29. MMU enables on the ZedBoard                          | 51 |

| Figure 30. The CPU1 wakes up on ZedBoard                        | 52 |

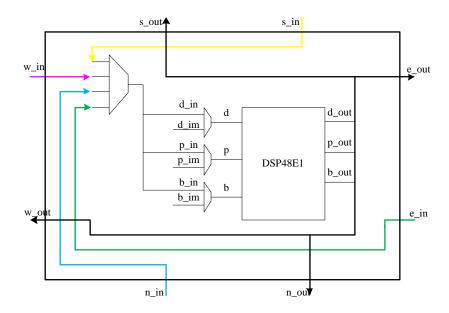

| Figure 31. Block Diagram of the Hybrid Computing Platform [26]  | 54 |

| Figure 32. Block Diagram of the Reconfigurable Region [26]      | 55 |

| Figure 33. State machine based Context Sequencer [26]           | 57 |

| Figure 34. Block Diagram of the Intermediate Fabric [26]        | 58 |

| Figure 35. The CB's organization                                | 58 |

| Figure 36. The PE's organization                                | 59 |

| Figure 37. Multiple Hardware and Software Task Scheduling [26]  | 64 |

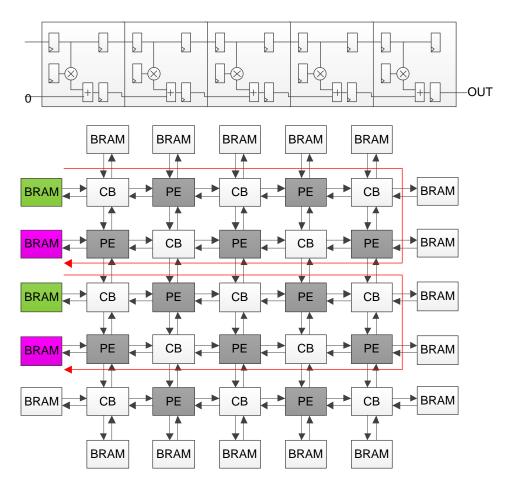

| Figure 38. Systolic FIR filter and its mapping to the IF [26]   | 65 |

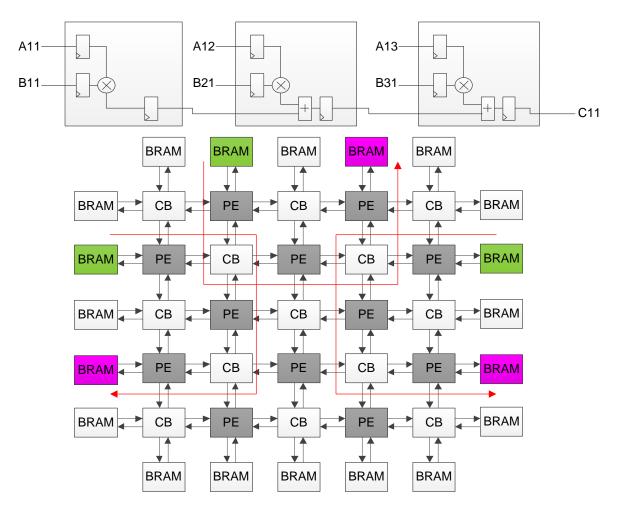

| Figure 39. Matrix Multiplication and its mapping to the IF [26] | 66 |

| Figure 40. Pseudo-code for IF configuration [26]                | 67 |

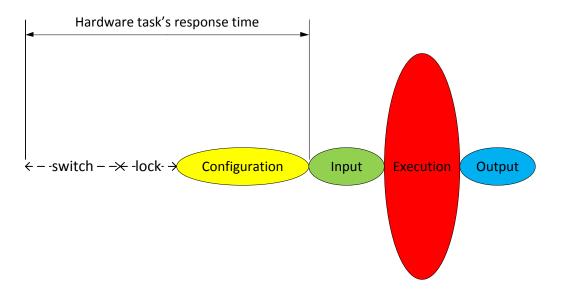

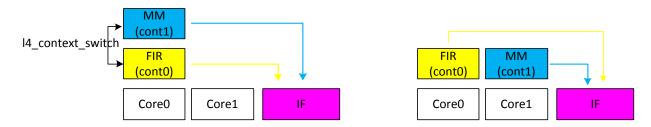

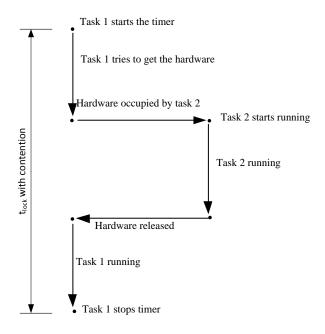

| Figure 41. A Hardware Task's organization                                                         | 68    |

|---------------------------------------------------------------------------------------------------|-------|

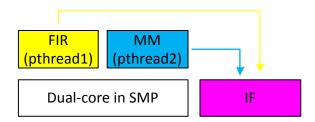

| Figure 42. 2 HW tasks on one core (Scenario 1) and 2 HW tasks on separated cores (Scenario        | 2).69 |

| Figure 43. Lock with contention                                                                   | 69    |

| Figure 44. Hardware Tasks run on CODEZERO and Embedded Linux                                      | 71    |

| Figure 45. IF's Idle Time                                                                         | 72    |

| Figure 46. Hardware Tasks mapping on Linux                                                        | 73    |

| Figure 47. Linux runs as a Guest OS on CODEZERO                                                   | 76    |

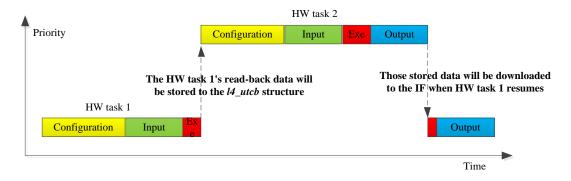

| Figure 48. Pre-emptive hardware context switching                                                 | 77    |

| Figure 49. PandaBoard                                                                             | 79    |

| Figure 50. CODEZERO overall configuration                                                         | 80    |

| Figure 51. CODEZERO kernel configuration                                                          | 80    |

| Figure 52. CODEZERO "Linux" container configuration                                               | 81    |

| Figure 53. CODEZERO configuration UI                                                              | 81    |

| Figure 54. CODEZERO boot sequence                                                                 | 82    |

| Figure 55. CODEZERO boots on PandaBoard                                                           | 83    |

| Figure 56. Bare-metal's application configuration                                                 | 84    |

| Figure 57. CODEZERO kernel starts and its container displays the messeage "Hello World!".         | 84    |

| Figure 58. The context switch application starts and runs                                         | 85    |

| Figure 59. Linux starts running on CODEZERO                                                       | 86    |

| Figure 60. The $\mu\text{C/OS-II}$ application starts creating many tasks in different priorities | 87    |

| Figure 61. Created tasks start executing                                                          | 87    |

| Figure 62. The μC/OS-II's scheduler switches amongst running tasks. Task with higher priority                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|

| appears more frequently by pre-empting other lower tasks                                                                                 |

| Figure 63. The overall configuration for two applications on CODEZERO88                                                                  |

| Figure 64. The container configuration for the first "Linux" application (physical area from 0x80000000 to 0x9d000000)                   |

| Figure 65. The container configuration for the second "Hello-world" application (physical area from 0x9d000000 to 0xa0000000)            |

| Figure 66. Two different containers of CODEZERO can start and display messages                                                           |

| Figure 67. The "Linux" application is booting in one container while timer interrupts and context switches happen in the other container |

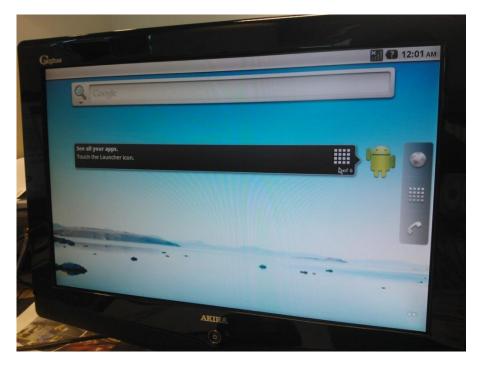

| Figure 68.The "Android" and "Linux" applications can start in two different containers of CODEZERO                                       |

| Figure 69. The "Android" starts and is displayed on the HDMI screen91                                                                    |

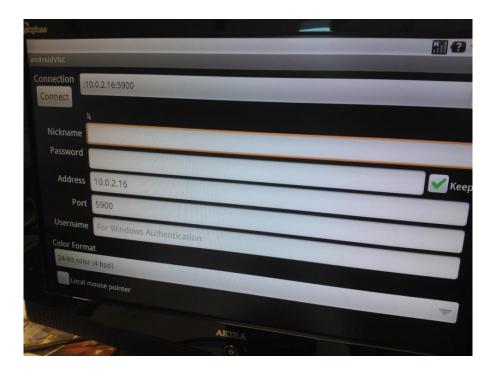

| Figure 70. The VNC application is used to switch between "Android" and "Linux"92                                                         |

| Figure 71. The VNC application on "Android"                                                                                              |

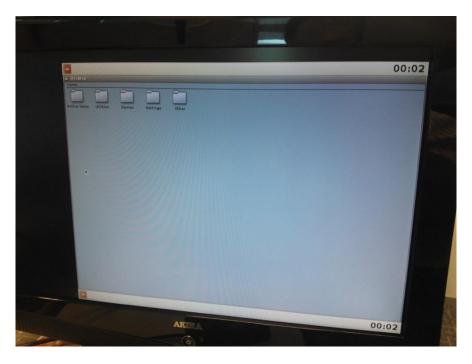

| Figure 72. The "Linux" appears on the HDMI screen after switching from "Android"93                                                       |

# Chapter 1

### Introduction

#### 1.1 Motivation

Motor vehicles today have a large number of electronic components, which control many parts of the car, such as the engine, brake assist system, airbag system, suspension system, information system, etc. Nowadays, more than 100 electronic control units (ECUs) are being used in a top end car. However, those ECUs just share a 20% mix of the automotive control system, while the other 80% is in charge of mechanical and hydraulic components and connections which link control components (e.g. gears, pedals and steering wheels) to the steering column and drive shafts, etc. In order to reduce system costs, one of the long term goals is to integrate many of the mechanical/hydraulic components to unified-electrical/electronic ones. However, the complexity of the user's requirements contributes to the increase in the number of ECUs since implementing new and complex functions needs additional ECUs, causing a cost increment, more power consumption, more heat dissipation, and more space consumption (e.g. communication). The introduction of multicore and hybrid architectures, such as FPGA-based reconfigurable computing, has resulted in the automobile industry proposing ECU consolidation [1-3] as a means to reduce some of these detrimental effects. ECU consolidation uses a (or several) centralized multicore processor(s) to replace many of the distributed ECUs.

ECU consolidation does have its own problems, in terms of robustness, determinism, predictability and dependability, particularly when the centralized multi-core executes both real-time tasks and common applications (such as entertainment or navigation) at the same time. To overcome this issue, the virtualization technique is considered, so that both real-time and non-critical applications can run in an isolated environment (i.e. separate operating systems (OS) with separate memory areas) on the same physical centralized computing platform. Moreover, as more computational intensive applications (e.g. intelligent driving, multi-media and network applications) are integrated into high end cars, the computational requirements increase. As a result, hardware accelerators for these applications can be adopted in the centralized platform to enhance the performance and processing abilities. Therefore, the

virtualization system should also be able to manage the reconfigurable logic to implement multiple hardware accelerators by taking advantage of a software-hardware (SW-HW) hybrid computing platform which contains a multi-core processor and an FPGA.

There are several existing embedded hypervisors or virtual machine managers on the market, some of which are certified for hard real-time systems. However, all of those hypervisors only virtualize the conventional general purpose microprocessor (the software part) without considering the FPGA (the hardware part). Thus, FPGA virtualization (e.g. FPGA resource abstraction, the general hardware accelerator interface, etc.) and its integration into a current hypervisor are important for ECU consolidation using a hybrid computing platform, and are the focus of this research project.

In this project we examine existing virtualization techniques for both conventional microprocessor based systems and for FPGA systems. Moreover, reliable and secure techniques for incorporating FPGA reconfiguration for application acceleration into the virtualized computing space will need to be developed. This includes both hardware designs on FPGA and software abstractions inside the hypervisor. Analysis of hardware virtualization using various benchmarks will be used to examine the hardware-dependent impact and to identify deficiencies, and hence develop approaches to further improve the hardware virtualization.

#### 1.2 Contribution

This thesis proposes a new approach to embedded virtualization by applying the microkernel-based hypervisor to the hybrid ARM – FPGA platform. It includes a modification of the microkernel-based hypervisor to the hybrid platform and support for an FPGA hardware accelerator for compute intensive applications. Based on examining, evaluating and analyzing the basic functionalities of CODEZERO, a specific hypervisor, we show how to manage the FPGA resources using a traditional hypervisor. That is to schedule a hardware task and to perform hardware context switching. Moreover, an FPGA hardware accelerator which can support the hardware context switch is developed. A prototype of the modified hypervisor and some preliminary experiments are then presented.

Part of the work carried out in this thesis has been published in [26].

### 1.3 Organization

In Chapter 2, a review of technical terminologies is presented in terms of embedded virtualization, microkernel, and hybrid platforms. Some user cases will be introduced to answer the question: why do we need to use the embedded virtualization technique? Moreover, some existing embedded hypervisors will be reviewed.

Chapter 3 describes the CODEZERO porting to the Xilinx Zynq 7000 platform (ZedBoard). The boot sequence of CODEZERO on the ZedBoard and some highlights of the porting work are discussed further.

The new hybrid platform for virtualizing both hardware and software components is presented in Chapter 4. Further modifications to CODEZERO to support the FPGA part of the hybrid platform are described. Experiments are performed to compare the performance between applications running on CODEZERO and on Embedded Linux. These results are presented and discussed.

The conclusions and recommendations for future work are given in Chapter 5.

# Chapter 2

# **Background**

### 2.1 Definitions and concepts

#### 2.1.1 Embedded virtualization

Virtualization on embedded systems has gained momentum since the appearance of the Motorola Evoke [4] in April 2009. Although virtualization on desktops and servers is mature, virtualization on embedded systems is not common, but is growing quickly. Due to their limited resources, virtualization on embedded systems needs different approach techniques from virtualization on desktops or servers. Embedded systems may use a real-time OS for embedded real-time applications, a general purpose OS for user interfaces and non-critical computing, or have no operating system at all. A server or desktop system just needs to run many virtual copies of the same or a similar OS, such as Linux or Windows [5]. Embedded virtualization is a more complex, but promising solution for more complex embedded systems, such as ECU consolidation, real-time industrial control, software complexity, safety, security and robustness, etc.

#### 2.1.2 Hypervisor or virtual machine manager

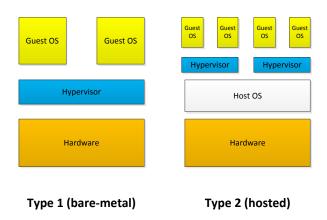

A hypervisor or virtual machine manager (VMM) is a middle layer which allows a number of guest OSs to run at the same time. There are 2 types of hypervisor, categorized as: type 1 and type 2, as shown in Figure 1. In type 1, the hypervisor runs directly on the hardware layer without the host OS, and is called a bare-metal hypervisor; whereas the hypervisor installed on a host OS, on which other guest OSs will run is a type 2 hypervisor, referred to as a hosted hypervisor. The bare-metal hypervisor controls hardware resources and manages one (or many) guest OS(s) running above it, so it produces less overhead than its hosted counterpart. However, the bare-metal hypervisor must have its own scheduler, and in fact, it works as a lightweight OS. Conversely, the hosted hypervisor only produces hardware emulation for its guest OSs, while the host OS does the resource allocation and the task scheduling. In the

embedded virtualization scenario, due to hardware resource limitations, the bare-metal hypervisor is preferable to the hosted hypervisor, which is more popular in desktop and server virtualization.

Figure 1. Type 1 (bare-metal) and Type 2 (hosted) hypervisor

#### 2.1.3 Para-virtualization versus full-virtualization

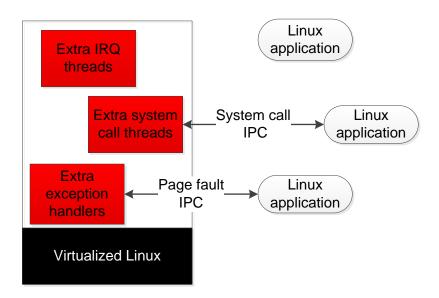

Para-virtualization is a virtualization technique that introduces a software interface between the guest OS and the hypervisor. The guest OS needs to be ported to the interface in order to run on the hypervisor. In the porting modification, all privileged instructions in the guest OS must be replaced by calls to the hypervisor [6]. Thus, instead of invoking a processor exception when an application tries to access resources which are not available, the guest OS calls to the hypervisor. After that, the hypervisor makes the necessary system calls to the processor to handle those instructions. In fact, the guest OS is treated as a normal application running on the hypervisor as shown as in Figure 2.

On the other hand, full-virtualization provides a complete simulation of the underlying hardware, in terms of instruction set, I/O peripherals, interrupts, memory access, etc. In full-virtualization, any standalone operating system can run successfully on a hypervisor as a guest OS without any modification. When the guest OS executes a privileged instruction or makes a system call, the hypervisor will trap that operation and emulate the privileged instruction or the system call as if the guest OS is running on a real hardware.

In summary, the para-virtualization technique introduces lower overhead and higher performance but requires more development cost and may contain more potential bugs than the full-virtualization technique running an unmodified guest OS. Again, due to the highly constrained hardware resource, it seems that the para-virtualization technique is more suitable than its counterpart in embedded virtualization.

Figure 2. Para-virtualized Linux

#### 2.1.4 Microkernel

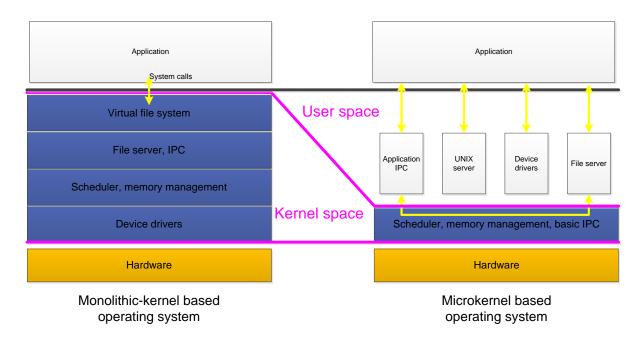

The microkernel is a minimal set of primitives to implement an OS. It just keeps a small number of very fundamental primitives (e.g. the scheduler, memory management, inter-process communication, etc.) in kernel space, while putting other parts, such as device drivers, the file system, networking, or so on, in user space. Originally, the microkernel concept was designed for more secure and reliable OSs, as an answer to the monolithic-kernel concept, which tried to implement all the OS's services in the kernel. However, the first two generations of microkernel-based OSs fell out of favor, because inappropriate implementations made them inefficient and inflexible [7]. Since 1995, when Jochen Liedtke proposed some new approaches to implement the microkernel and improved its overall performance [7, 8], the microkernel has become more popular. The comparison between structures of monolithic kernel and microkernel is shown in the Figure 3.

Figure 3. Monolithic-kernel based OS versus microkernel based OS

There is some research which found that the microkernel is very suitable for use as a hypervisor for embedded virtualization [9, 10]. However, most microkernels just support para-virtualization, because of its better performance and less overhead. It also requires more effort to modify the guest OS to run on top of a microkernel based hypervisor, and can introduce hidden bugs. Moreover, it makes the update of the guest OS more difficult, expensive and risky.

#### 2.1.5 Benefits of virtualization on embedded systems

When considering some of the attributes of microkernels, such as good isolation, fast intercommunication, real-time capabilities, etc., embedded virtualization has some obvious benefits, including:

- Increasing the system's reliability by isolating the physical memory regions for each guest OS without interfering with each other

- Increasing the software life cycle by enabling reuse of old and legacy software

- Preventing fault propagation between separated domains, making the system more robust and reliable

- Enabling efficient task scheduling and intercommunication between guest OSs

- Reducing hardware cost, software complexity and power consumption

Some of embedded virtualization's practical examples are listed below.

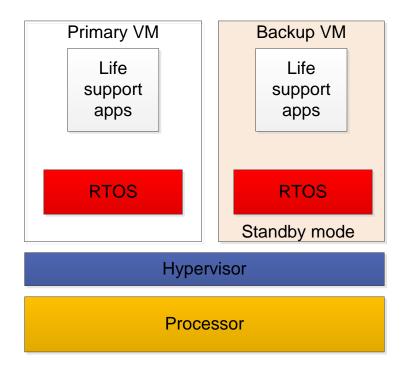

**Safety-critical backup:** Some safety-critical systems may need to keep a backup function and replace the primary function immediately when the system fails and needs to be rebooted. A virtualization technique can be applied to this scenario by creating a backup virtual machine and putting it into standby mode. In this way, a system crash on the primary virtual machine will not lead to a catastrophic result because the backup virtual machine can take over immediately [11] as in the Figure 4.

Figure 4. Primary VM + Backup VM

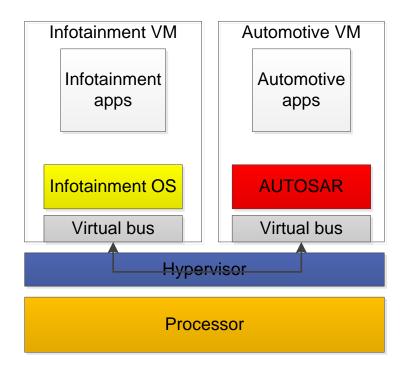

**OS** isolation: An automotive OS, for example AUTOSAR, coexists with an infotainment OS, such as Linux or Windows, on the same ECU. The virtualization technique enables safe integration by creating two divided virtual machines, one for each OS. The benefits are: reduced hardware cost and software complexity and improved robustness and reliability [5] as shown in Figure 5.

Figure 5. Infotainment VM + Automotive VM

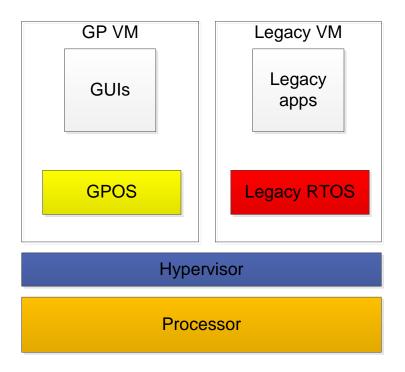

**Software reuse:** A change in hardware often requires a change in software. In the embedded systems domain, some applications need to be completely rewritten. Rewriting and testing code just for a new hardware platform is costly and wasteful. Virtualization can reduce the overall cost by executing the legacy OS and its applications on a virtual machine running on the new hardware platform as in the Figure 6, thus extending the life cycle of the software.

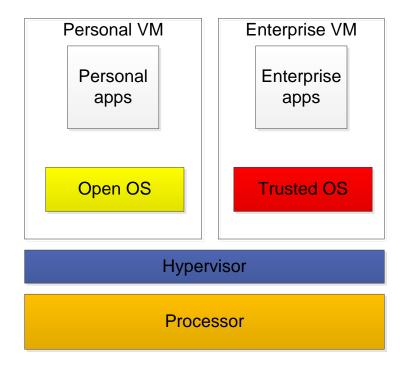

**Improve security:** A corporation may need to provide personnel with a secure mobile device (e.g. a mobile-phone or a tablet) in order to let them access the enterprise's internal database. In this case, virtualization can be used to create two virtual phones on a unified physical device: a personal virtual phone on an open OS and an enterprise virtual phone on a trusted OS, both of which are running at the same time on the same physical platform. The enterprise virtual phone is managed by the corporation's IT staff, while the personal phone is fully controlled by the user as in Figure 7. This isolation keeps sensitive data safe and secure, even if the user installs a low-security application onto the personal phone [5].

Figure 6. General purpose VM + Legacy VM

Figure 7. Personal  $VM + Enterprise\ VM$

#### 2.1.6 Constraints for embedded virtualization

There are a number of constraints imposed on an embedded hypervisor.

Code size: The code size of an embedded hypervisor must be small due to the limited memory in most embedded systems. Some popular embedded hypervisors are only around ten thousand lines of code [12]. A bigger size means the system needs more memory, leading to more hardware cost and more power consumption. In addition, for safety-critical systems, which need to have every line of code analyzed by experts, a bigger size means more expense and a bigger potential threat. Server hypervisors usually have several million lines of code, and are not suitable for embedded systems. The code size requirement is one of the most important reasons why the microkernel is preferable as an embedded hypervisor.

**Determinism and latency:** Some applications running on an embedded hypervisor are real-time applications. These applications not only need to be responded to quickly, but also within a bounded time. Therefore, the embedded hypervisor must be able to handle an interrupt within a very short time, as well as execute its internal operations within a deterministic time [13].

**Security:** With the small code size, an embedded hypervisor can easily be validated and shown to be bug free [14]. Some hypervisor vendors have certifications to show that their products are bug free. This is very important because some of the applications of embedded virtualization are safety-critical systems that could cause catastrophic damage when a failure occurs. The microkernel approach is very helpful in keeping the hypervisor simple and small, because it outsources most of the complex and less trusted system parts to user space. Thus, the microkernel is the minimal portion running in privileged mode, conducting processor and memory management, and serving as the *trusted computing base* (TCB).

**Isolation:** The ability to isolate a guest OS from another one is also essential for a microkernel-based hypervisor. This way, it not only prevents fault propagation from one domain to another, but also improves the security and reliability of the whole systems. In a microkernel-based hypervisor, each guest OS will be allocated to a typical memory space and only privileged (kernel controlled) inter-process communication (IPC) can be used to communicate cross-domain.

**Communication:** The isolation and security requirements for a microkernel-based hypervisor need a secure and efficient mechanism to communicate between different domains or guest OSs residing in divided memory spaces. Without this communication mechanism, the hypervisor cannot share or synchronize data between multi-tasks, threads or guest OSs.

**Scheduling:** Embedded virtualization has two levels of scheduling. The first scheduling level is in the guest OS to schedule tasks running on it. The second is in the microkernel to choose which virtual machine or guest OS will be run. There are two commonly used algorithms for the microkernel's scheduler: round-robin and fixed priority. The later one is to support real-time capability, which allows a critical task in a higher priority domain to run whenever it is available.

## 2.2 Existing virtualization techniques

There are a number of commercial embedded virtualization products currently available.

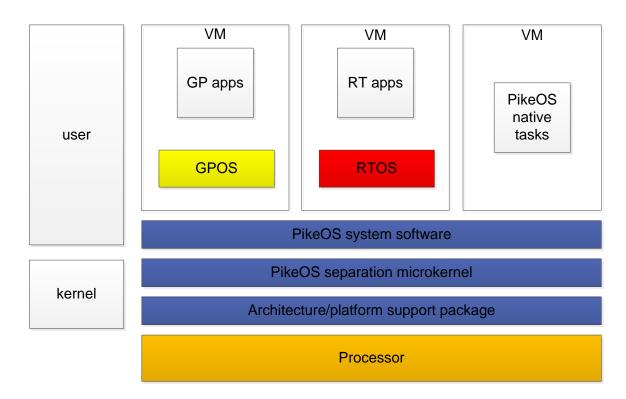

**PikeOS:** One of the most popular microkernel-based hypervisors is PikeOS [15], which is used widely for some safety-critical applications in the avionics industry. The PikeOS' structure is shown in Figure 8. With embedded virtualization, old and legacy applications can coexist with later applications on the same hardware platform, but in separated virtual machines. PikeOS supports a number of architectures, including ARM, x86, PowerPC, SuperH, etc... A number of guest OSs, application programming interfaces and runtime environments, for example PikeOS native interfaces, Linux, Android, ARINC 653 APEX, POSIX, Real-time Java are supported by PikeOS. As PikeOS uses the para-virtualization technique, guest OSs need to be modified from their original versions to run in a PikeOS virtual machine. Although widely used in the avionics industry, PikeOS is actively targeting the automobile industry. COQOS [16], which can virtualize both Android and AUTOSAR on the same platform, is a commercial product based on the PikeOS structure.

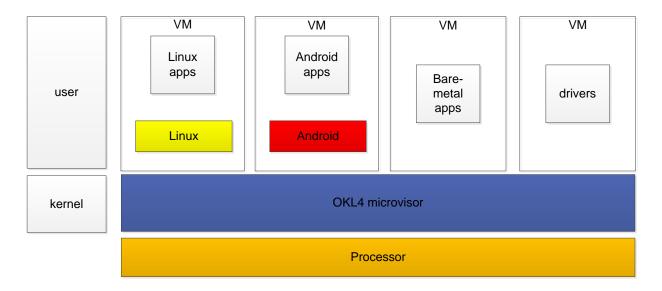

**OKL4:** OKL4 [17] was developed by Open Kernel Labs (OK Labs). This product is very popular in the consumer electronics area. It focuses on security applications to create more secure devices used in business mobile phones, set-top-boxes or network routers. As with other products in the L4 family, OKL4 only supports the para-virtualization technique. It means that guest OSs such as Linux, Android, etc., must be adapted in order to run on top of OKL4. Many guest OSs have been released by OK Labs, including, OK:Linux, OK:Android and OK:Symbian. However, till now, there is no industrial example which uses the OKL4 microkernel for safety-critical applications. The structure of OKL4 is summarized in Figure 9.

Figure 8. PikeOS's structure

Figure 9. OKL4's structure

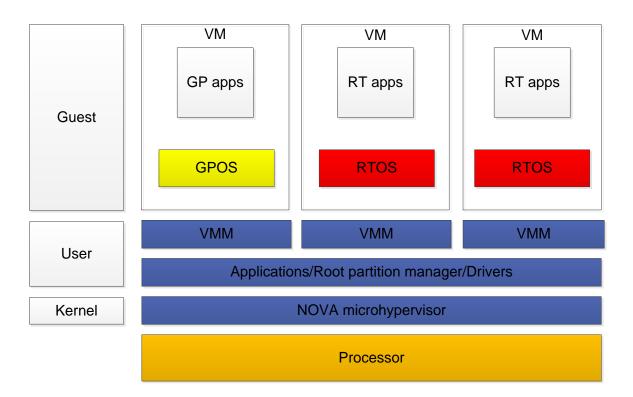

**NOVA:** NOVA [18] is a third generation microkernel, because it supports full-virtualization. Guest OSs do not need to be modified to run on the NOVA hypervisor. It takes less time and effort to port

applications to one of its virtual machines, as well as reducing the number of potential bugs when modifying them. However, NOVA has to add one more middle layer, which consists of a root partition manager, device drivers and VMMs, into user space. In this way, NOVA can keep its kernel small and reliable, but introduces more overheads, as it has to emulate the hardware for execution of the guest OSs' privileged instructions. The Figure 10 displays the NOVA's structure.

Figure 10. NOVA's structure

The L4 Microkernel: The L4 microkernel was first introduced by Jochen Liedtke [7] and provides 3 key primitives to implement policies: address spaces, threads, and IPC. With the address space concept, memory management and paging can be implemented outside the microkernel, based on granting, mapping and unmapping, which are kept inside the kernel [19]. Threads are used to support multitasking, while IPC creates a mechanism for communication between threads in divided address spaces. Moreover, IPC is used to control the executing flow's changes between protected areas, to control data transfer among them and to entrust resources with mutual agreement between senders and receivers [10]. With this simple IPC primitive, the microkernel can minimize the necessary security mechanisms as well as the kernel complexity and code size. The smaller the code size, the fewer errors the kernel can introduce and

the smaller the cache footprint. This means that the system is cheaper, smaller and has less power-consumption.

In order to achieve the necessary performance and flexibility, the microkernel has to be optimized based on the processor's architecture to take advantage of the specific hardware. Because one processor's architecture has some tradeoffs compared with another, the microkernel should be the lowest level of OS on the hardware without any other abstraction. This means that the microkernel is hardware-dependent and is inherently not portable [7].

The L4 microkernel can also support real-time applications concurrently with general-purpose applications by using cache partitioning and the IPC model. Because real-time tasks need to meet their deadlines, the required resources must always be allocated and scheduled. Cache partitioning means the microkernel uses the main-memory manager (pager) to partition the second-level cache among various real-time tasks and to isolate them from timesharing ones. This helps to avoid cache interference and cache miss, thus improving the predictability and the performance for real-time tasks. With this IPC model, a server can easily pre-allocate kernel and user resources, threads and stacks, dedicated to specific applications [8].

#### 2.3 CODEZERO

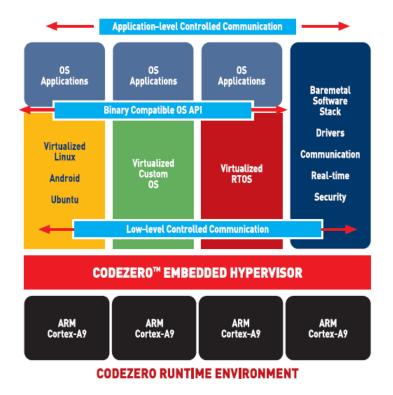

CODEZERO [12] is developed from the L4 microkernel, and follows the latest concept and research principles on microkernel design [15]. The code size is about ten thousands of lines of C code, and its APIs consist of twelve main system calls. Therefore, CODEZERO is simple, small and efficient, compared to other L4 microkernels. Figure 11 summarizes the CODEZERO's structure.

CODEZERO is able to schedule threads to multiple cores, on both symmetric multi-processor (SMP) and asymmetric multi-processor (AMP) architectures. In SMP, CODEZERO delivers threads to any core on the platform without any restriction on which core is running which thread. It helps to utilize computing performance and power. In addition, for the determinism requirements of real-time capabilities, CODEZERO can also schedule specific threads onto specific cores, supporting the AMP architecture. Additionally, CPU time-slices can be adjusted with demand.

Figure 11. CODEZERO's structure [12]

CODEZERO supports kernel preemption for real-time tasks. Moreover, CODEZERO keeps the interrupt handler as small as possible. It just clears the interrupt flag and then calls the child thread to handle the interrupt function. Thus, both the interrupt threads as well as the other threads can be scheduled and pre-empted whenever another more critical event happens.

#### 2.3.1 System partitioning by using containers

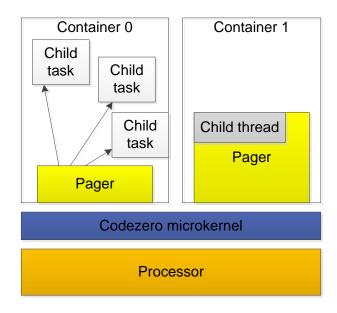

CODEZERO introduces the concept of a container for virtualization on embedded systems. A container provides an isolated virtual environment with its own set of resources such as threads, address spaces, and memory resources, as in the Figure 12. CODEZERO uses a fixed priority scheduler to schedule which container will be run based on its priority. This is helpful when an RTOS is run concurrently with a GPOS, because tasks in the RTOS's domain will always be scheduled before tasks in the GPOS's domain.

Figure 12. CODEZERO's containers

At the beginning, there is only one privileged task called a pager running in each container. The pager then creates further children tasks running in their own virtual memory spaces to produce a multitasking environment inside its container. This model is a typical setup for a virtualized guest OS. For example in container 0 in Figure 12, the kernel acts as the pager and its applications are child tasks.

Another model is for a bare-metal or self-contained application, where the application is the pager itself, as shown as in container 1 in Figure 12. The pager can create multiple children threads in the same address space and then works as a standalone application on the hardware. Those standalone multithreaded applications can be used to test hardware devices or to develop a lightweight RTOS.

The pager task possesses all privileged capabilities inside the container. It can create and manage threads, because it owns the thread control, and exchange register capabilities. Moreover, a pager can map a physical address to a virtual address for its own address space and the address space of its children tasks, because it also has possession of both physical and virtual resources. Because the pager only has rights to its own container, it is very easy and simple to manage isolation between containers.

Capability is a security mechanism implemented in a CODEZERO's container. It represents a right to access to kernel-managed resources in terms of system calls, memory regions, memory pools, and IPCs. Capabilities can be possessed by all tasks inside the container or by some of them. Children tasks,

as shown Figure 13, own a mutex pool capability, so they are allowed to communicate with any thread inside the container via IPC.

Figure 13. Capabilities inside a container

#### 2.3.2 Communication by IPC and shared memory

IPC requires the User Thread Control Block (UTCB), which is defined for every unique thread on the system, as a message buffer. Moreover, this UTCB can be used as thread-local storage. Typically for the ARM architecture, UTCBs are 64 word memory blocks.

IPC is implemented as a synchronous communication mechanism in CODEZERO. There are three types of IPC, namely: short IPC, full IPC and extended (long) IPC. The short IPC is the most frequently used method of IPC between user space threads. Two communicating threads only transfer their primary message registers, which are registers that are capable of mapping onto real registers in the system. For example in an ARM system, they are MR0-MR5, which could map onto R3-R8 on real hardware registers. The whole UTCB buffer with 64 words is transferred among threads in full IPC, whereas a transferred message might be up to 2KB in extended IPC.

Figure 14. Inter-process communication inside and between containers

Children tasks in a container can communicate with their pager and each other. With appropriate capabilities, a child task can communicate with tasks in different containers via inter-container IPCs, as in the Figure 14.

In a shared-memory mechanism, two pagers in different containers may have the same physical address, and therefore can communicate each other. This mechanism depends on the relevant physical and virtual memory capabilities they possess.

#### 2.3.3 Virtualization

CODEZERO supports the para-virtualization methodology, in which the guest OS kernel is abstracted away from the hardware details. It means that the guest OS kernel's privileged instructions are replaced by calls to the microkernel. In the CODEZERO runtime environment, the guest OS kernel works as the pager in a container with capabilities to create and manage applications, as shown in the Figure 15. The guest OS kernel's access rights are limited by the boundaries of that container.

Figure 15. Para-virtualized Linux on CODEZERO

# 2.4 Summary

In this chapter the concept of embedded hypervisors was introduced. A review of the state of the art in embedded hypervisors and an analysis of one on the newer embedded hypervisors (CODEZERO) were conducted.

This then develops the groundwork for my current work which involves porting CODEZERO to a hybrid ARM-FPGA platform described in Chapter 3. This also leads into, and becomes the focus of my work which will include the first steps in the virtualization of the FPGA hardware on the Zynq 7000 platform which is described in Chapter 4.

# **Chapter 3**

# Porting CODEZERO on ZedBoard

This chapter introduces the Xilinx Zynq 7000 extensible processing platform, and the possibility of adding virtualization support for FPGA-based hardware tasks. It then goes on to describe the porting of the B-Labs CODEZERO hypervisor to the Xilinx Zynq 7000 family of FPGAs. The starting point for the CODEZERO Zynq 7000 port is CODEZERO version 0.5 for the Texas Instruments OMAP4430 processor on the PandaBoard platform [20]. The target platform is the ZedBoard [21] based on the XC7Z020-1CLG484C, Zynq-7000 SoC [22]. Throughout this chapter we will use the terms "ZedBoard" as well as "Zynq 7000 platform" interchangeably. The CODEZERO port to the ZedBoard was a joint effort, with some of the initial work being done by author 3 of [26].

# 3.1 Virtualizing the Xilinx Zynq 7000 extensible processing platform

The Zynq 7000 extensible processing platform (EPP) is a new system-on-chip (SoC) introduced by Xilinx in 2012. It integrates a dual-core Cortex-A9 processor, a Xilinx 7000 series FPGA [23] and some common peripherals onto a single die. The powerful dual-core Cortex-A9 processor is for general-purpose applications, and the programmable logic is for users to develop new peripherals, hardware accelerators or application specific processing units. Moreover, on a conventional two-chip platform (processor + FPGA) which communicate each other via the I/O port, the performance is limited due to communication latency, I/O bandwidth and power budget. However, the single chip Zynq 7000 is not limited by these factors and is able to achieve a much higher computing performance. This approach gives the Zynq 7000 chip a chance to become a very customized, flexible and powerful processing platform. The characteristics of the Zynq 7000 platform are given in Table 1 and Figure 16.

Table 1. Zynq 7000's specifications [23]

| Processing system         |                                                                   |  |

|---------------------------|-------------------------------------------------------------------|--|

| Processor                 | Dual-core ARM Cortex-A9 up to 1GHz                                |  |

|                           | ARMv7-A architecture with TrustZone ® security and Thumb®-2       |  |

|                           | instruction set                                                   |  |

| Memory                    | 32 KB Level 1 and 512KB Level 2 caches                            |  |

|                           | On-chip boot ROM                                                  |  |

|                           | 256 KB on-chip RAM                                                |  |

|                           | External memory supports multiprotocol dynamic memory controller, |  |

|                           | static memory interfaces                                          |  |

| Peripherals               | USB, CAN, SPI, UART, I2C, GPIO, etc.                              |  |

| Interconnect              | ARM AMBA® AXI bus system for data transfer between processing     |  |

|                           | system and programmable logic                                     |  |

| Programmable logic        |                                                                   |  |

| Configurable logic blocks | Look-up tables (LUT), flip-flops (FF), cascadeable adders         |  |

| Memory                    | 36 Kb block RAM                                                   |  |

| DSP blocks                | 18x25 signed multiply, 48-bit adder/accumulator, 25-bit pre-adder |  |

| Other peripherals         | Programmable I/O blocks                                           |  |

|                           | 16 receivers and transmitters with up to 15 Gb/s data rate        |  |

|                           | Two 12-bit analog-to-digital converters                           |  |

Figure 16. Zynq 7000's organization [23]

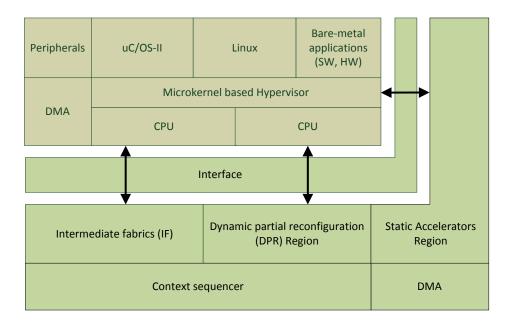

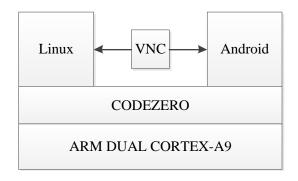

Both the microkernel-based hypervisor and the hybrid platform open a new horizon for applications on embedded systems. We can use the microkernel to virtualize many different kinds of OSs and SW-HW co-designed applications running on them, with the FPGA part of the hybrid platform used for application acceleration. The acceleration could be for the virtualization itself or for some compute-intensive applications running on one of the guest OSs. The challenges are not only to implement these hardware accelerators, but also how to abstract and integrate those new hardware parts into the existing microkernel without affecting the system's performance.

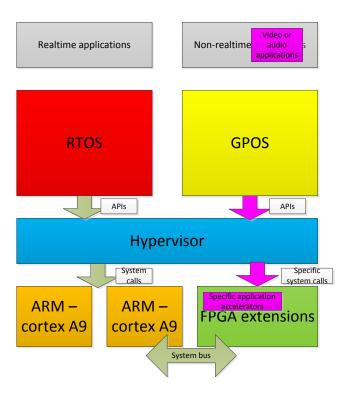

Hardware accelerators and SW-HW application partitioning is relatively mature and can be implemented using the conventional FPGA resources. However, enabling hardware acceleration to work with a hypervisor in a virtualized environment is not a simple procedure. Because the microkernel is small, efficient and simple, increasing the number of APIs should be avoided as much as possible. This means that we have to utilize existing APIs to abstract new hardware functions and modify the guest OS to use those abstractions. The overheads from data transfer between processing system and programmable logic need to be considered and analyzed carefully. The initial idea of the platform for SW-HW virtualization is shown in the Figure 17.

Figure 17. Initial idea for SW-HW virtualization platform

### 3.2 Booting CODEZERO on the ZedBoard

#### 3.2.1 The overall boot sequence

In the ZedBoard, the NAND flash, NOR flash, SD card, Quad-SPI, and JTAG are five possible boot sources. The master boot method uses one of the first four boot sources in order to load the external boot image from non-volatile memory into the on-chip memory (OCM). In the slave boot mode, an external host PC uses the JTAG connection to load the boot image into the processing system (PS) while the PS CPU is not executing. The boot sequence of the ZedBoard has 3 stages: stage 0, stage 1 and stage 2 (optional). Its boot sequence is summarized in Figure 18.

In stage 0, a hard-coded boot program stored in ROM executes and initializes some basic peripherals such as the NAND flash, NOR flash, the SD card and the Quad-SPI and PCAP interfaces immediately after power-on reset (POR). This boot program runs on the primary CPU and is in charge of loading the stage 1 boot image. Other peripherals, such as DDR, CLK, MIO, etc..., are not initialized in this stage. They are initialized in stage 1 or later stages.

The first stage boot-loader (FSBL) configures the CLK, DDR, and MIO for the PS part. Moreover, it also programs the programmable logic (PL) part if the bit-stream is provided. Then, the second stage boot-loader (SSBL) or bare-metal application will be loaded into DDR memory. In addition, the FSBL also invalidates the instruction cache and disables the cache and MMU for the U-Boot in the later stage. Finally, it gives the control to the SSBL or the bare-metal application.

Currently, we do not have the bitstream downloaded automatically in this first stage boot, but we can compile that bitstream with the FSBL later by using the Xilinx SDK tool [24].

The second stage boot-loader (SSBL) is optional and user-designed (for example U-Boot), but it is necessary to bring the operating system from the permanent storage media into memory. It provides some useful features, such as transferring, loading and executing kernel images from flash memory, USB, serial port, and Ethernet. Moreover, the boot-loader can initialize hardware, such as the DDR or serial port, which is very important for booting or debugging.

Figure 18. Boot sequence of the ZedBoard

In the case of the CODEZERO boot on the ZedBoard, we use the same U-Boot as is used to boot the Linux kernel on ZedBoard [25]. The U-Boot command *mmcinfo* is used to initialize the SD card.

#### ./mmcinfo

After that, the *fatload* command is used to load the kernel image (the *uImage* file) from partition 0 of the SD card to the beginning of the main memory (the main memory starts from 0x0 in the ZedBoard).

#### ./fatload mmc 0 0 uImage

Then, another command *bootm* is executed from the specified memory where the final image is stored.

#### ./bootm 0

U-Boot automatically decompress the final image file, re-allocates the CODEZERO loader image in the final image to the address 0x02000000 which is the entry point address stored in the ELF file header. Finally, the execution jumps to the entry point address of the CODEZERO loader to start CODEZERO (the label \_start in the file crt0.S). The CODEZERO kernel and loader start addresses are configured by the user in the compilation step according to the Zynq 7000 hardware manual, because

these addresses are different across various platforms. The configuration step and CODEZERO's final image layout will be described later. The stage 2 boot process is shown in Figure 19.

```

ll Tatload mmc 0 0 uImage

reading uImage

422484 byter and zed-bootx bootm 0

## Booting Kernel from Legacy Image at 00000000 ...

Image Name: final.elf

Created: 2013-06-18 3:47:21 UTC

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size: 422420 Bytes = 412.5 KiB

Load Address: 02000000

Entry Point: 02000000

Verifying Checksum ... OK

Loading Kernel Image ... OK

OK

Starting kernel ...

cuijinbird

copyright from NUT

ELF Loader: Loader image size: 412KB, placed at physical 0x2000000-0x2067214

```

Figure 19. The stage 2 boot

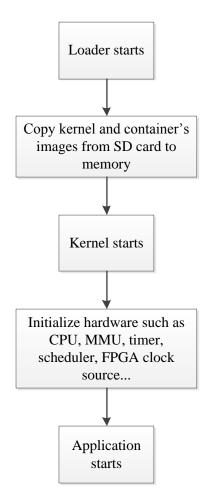

CODEZERO starts after the U-Boot command *bootm* has executed. Its boot sequence is displayed in the Figure 20. The CODEZERO loader will first start to load the CODEZERO kernel and user container images, then the CODEZERO kernel initialization will continue.

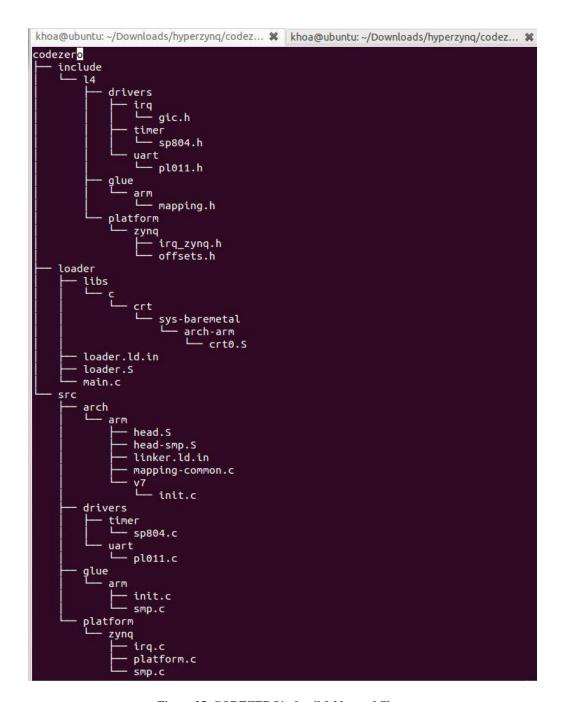

### 3.2.2 CODEZERO's folder structure and final image layout

CODEZERO's folder structure is illustrated to provide a better understanding of CODEZERO's boot sequence and the necessary modifications. The entire CODEZERO source code consists of three parts, as shown in Figure 21: the CODEZERO loader, the kernel, and the user containers. In this chapter, we only describe the CODEZERO loader and CODEZERO kernel, as user containers are not affected heavily by the target platform. The *loader* folder has the source code for the loader. CODEZERO's kernel source code is contained in the folder *src* and includes subfolders *arch* for architecture-specific functions, *drivers* for peripherals' device drivers, *glue* for architecture-generic function, and *platform* for platform-specific functions. The *include* folder contains all related header files for drivers, architectures, platforms, CODEZERO's structures and APIs. The contents of these three folders are modified during the porting process.

Figure 20. CODEZERO's boot sequence

Figure 21. CODEZERO's shortened folder structure

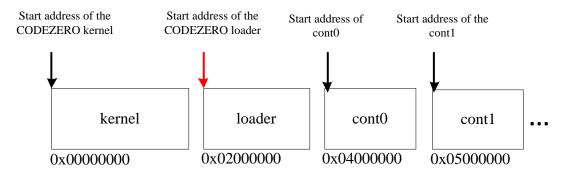

The CODEZERO loader, kernel and user containers are compiled independently to generate several separated binary images (*loader.elf* for the CODEZERO loader, *kernel.elf* for the CODEZERO kernel and

*contX.elf* for the user containers). At the final stage of the entire CODEZERO compilation the separated images are merged and compressed, if applicable, into the final image (the *uImage* file).

Figure 22 shows the CODEZERO final image layout on the Zynq 7000 platform, with the CODEZERO kernel start address at 0x0, the loader start address at 0x02000000 and with user cont0 and cont1 at 0x04000000 and 0x05000000, respectively.

Figure 22. CODEZERO final image layout on ZedBoard

The start addresses of the CODEZERO loader, kernel and user container images are stored in separated linker script files (*kernel.ld* for the kernel compilation, *loader.ld* for the loader image and *linker.ld* for the container images) and are defined by user configuration.

The "make menuconfig" command is used to configure the CODEZERO kernel and loader start addresses as shown in Figure 23. The start address of each user container image is set by changing the parameters PHYSMEM\_START and PHYSMEM\_END in the file *config.h* as shown in the Figure 24.

```

Kernel options

Arrow keys navigate the menu. <Enter> selects submenus --->.

Highlighted letters are hotkeys. Pressing <Y> includes, <N> excludes,

<M> modularizes features. Press <Esc> to exit, <?> for Help, </>

for Search. Legend: [*] built-in [ ] excluded <M> module < > module

(2) Maximum number of supported containers

[ ] Disable preemption

(1000) Scheduler ticks per second

(0x0) Kernel physical memory

(0x2000000) Loader physical memory

1 Disable I-Cache

] Disable D-Cache

[ ] Virtual Timer irq

Ubuntu One

<Select>

< Exit >

< Help >

```

Figure 23. Kernel and Loader start addresses configuration

```

#define VIRTMEM_START 0xc0000000

#define VIRTMEM_END 0x4000000

#define PHYSMEM_START 0x4000000

#define CPO_AFFINITY 0

```

Figure 24. Container memory area configuration

The CODEZERO loader and CODEZERO kernel initialization are critical parts for the ZedBoard port, as these two parts are hardware-dependent. Figure 25 shows the folder structure and the files that have been modified during the porting process.

Figure 25. CODEZERO's detail folder and file structure

### 3.2.3 CODEZERO loader porting

The loader loads the kernel and container images to the appropriate memory locations, then initializes the UART and finally jumps to the kernel section. Loader routines and functions that have been modified during the porting process are located in the *loader* folder, and are described in Table 2.

Table 2. The loader folder's file description

| File name and location                         | Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| loader/libs/c/crt/sys-baremetal/archarm/crt0.S | Contains the entry point's function of the loader section, checks the memory offset if the loader image is on correct memory location, if not then calls the function <code>loader_copy</code> in the file <code>loader/main.c</code> to copy the loader image on correct memory location, initializes the UART for debug purpose, then jumps to the <code>main</code> function in the <code>loader/main.c</code> file |

| loader/loader.ld.in                            | Defines the memory layout of the loader image, points out the entry point _start label and links the start physical address (CONFIG_HYP_LOADER_PHYS_START, configured in the compilation step) to that label                                                                                                                                                                                                           |

| loader/loader.S                                | Defines which image file should be loaded in case image compression or non-compression                                                                                                                                                                                                                                                                                                                                 |

| loader/main.c                                  | Copies the kernel and container images on appropriate memory locations, loads the kernel entry point, then jumps to the kernel section                                                                                                                                                                                                                                                                                 |

The \_start label is the entry point of the loader section according to the linker description file. Then the \_start function in the file loader/libs/c/crt/sys-baremetal/arch-arm/crt0.S is executed first to check the memory offset. If the loader image is at the correct physical memory location, which is defined by the user, as different platforms require different CODEZERO loader and kernel address offsets, via "make menuconfig" as mentioned above. If the memory location is not correct, it will reallocate that image to the corresponding memory location. After that, the UART is initialized with the base register address according to the Zynq 7000 hardware manual. This initialization is one of the most important steps in this stage because the serial port is crucial to debug further. Here we need to rewrite the UART driver for this purpose, which is detailed in Section 3.3.2. The main function in the file loader/main.c is executed to load and decompress kernel and container's images to memory. Finally, the loader jumps to the kernel's start address (the \_start procedure in src/arch/arm/head.S) for further CODEZERO kernel initialization.

### 3.2.4 CODEZERO kernel initialization porting

The kernel initialization starts after the loader finishes. This sequence will initialize the primary CPU core, enable the MMU, set up CODEZERO's identical structures and initialize the platform peripherals. Because CODEZERO's high-level structures such as UTCB, KIP, scheduler and other APIs

are hardware-independent, we do not need to touch them in this porting work. Table 3 describes some files which we have changed in the CODEZERO kernel source code.

Table 3. The src folder's file description

| File name and location        | Function                                                                                                                                                                                                                                                                                             |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| src/arch/arm/head.S           | Contains the kernel entry point's function; disables MMU, I-cache, D-cache, Write buffer and Branch prediction in the primary CPU for later initialization; backs up general registers' values into stack, and then jumps to the <i>start_kernel</i> function to initialize the platform peripherals |  |

| src/arch/arm/head-smp.S       | Contains the entry point's function for the secondary CPU; disables MMU, I-cache, D-cache, Write buffer and Branch prediction in that secondary CPU for later initialization; and jumps to the <i>smp_secondary_init</i> function to initialize the secondary CPU core                               |  |

| src/arch/arm/linker.ld.in     | Defines the memory layout of the kernel image, calculates the offset between the configured CONFIG_HYP_KERNEL_PHYS_START address and the KERNEL_AREA_START address, then maps the kernel's sections on right memory locations                                                                        |  |

| src/arch/arm/mapping-common.c | Contains some common and abstracted low-level page-table functions between v5 – v7 ARM architectures                                                                                                                                                                                                 |  |

| src/arch/arm/v7/init.c        | Contains specific system initialization for v7 ARM architecture                                                                                                                                                                                                                                      |  |

| src/glue/arm/init.c           | Contains common initialization routine between v5 – v7 ARM architectures                                                                                                                                                                                                                             |  |

| src/glue/arm/smp.c            | Contains the secondary CPU's wake-up and initialization functions                                                                                                                                                                                                                                    |  |

| src/platform/zynq/irq.c       | Contains generic irq handling for specific Zynq 7000 platform                                                                                                                                                                                                                                        |  |

| src/platform/zynq/platform.c  | Contains the specific platform initialization for Zynq 7000 platform                                                                                                                                                                                                                                 |  |

| src/platform/zynq/smp.c       | Contains SMP related definitions for Zynq 7000 platform                                                                                                                                                                                                                                              |  |

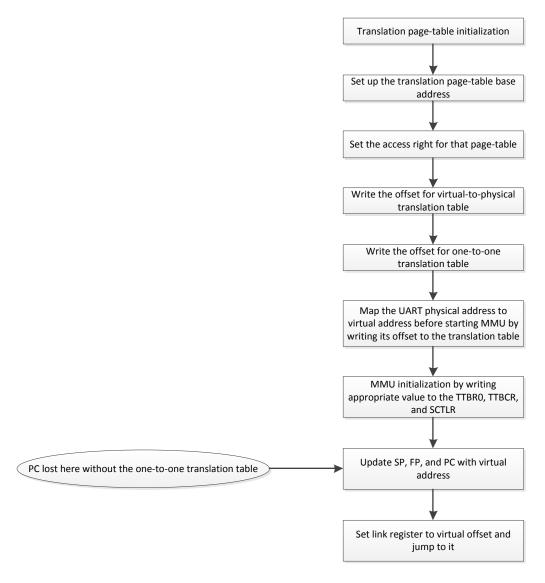

CODEZERO's kernel starts from the \_start procedure, specified in src/arch/arm/head.S, after the loader copies the kernel and container images to the correct memory location. It uses the start\_kernel function (file src/glue/arm/init.c) in order to initialize the primary CPU, because different ARM architectures have various routines to set up the CPUs. Moreover, the kernel will initialize the page tables (the function init\_kernel\_mappings, in src/arch/arm/v7/init.c) and wake up the MMU (the function start\_virtual\_memory, also in src/arch/arm/v7/init.c) since it was disabled in the stage 1 boot process. We will describe this issue in detail in the next section.

Several CODEZERO structures need to be initialized and mapped into user-space in this stage for further operations, for example the User-space Thread Control Block structure, *l4\_utcb*, Kernel Interface Page structure, *l4\_kip*, guest's shared memory page and system-call jump-table page. As this step is hardware-independent, we will not discuss it further.

Other platform peripherals, such as the timer, scheduler, and interrupt controller, are set up and mapped to the virtual address area by the function *platform\_init* in *src/platform/zynq/platform.c*. The timer and GIC device drivers need to be rewritten as described in the next section.

In the next step, if dual-core mode is configured, we need to wake up the second CPU core by calling the function  $smp\_start\_cores$  in glue/arm/smp.c. This function needs to be changed as the Zynq 7000 secondary CPU wake-up procedure is different from the PandaBoard's one. This issue will also be discussed further in the next section. After finishing the hardware and kernel's initialization, the kernel starts the timer and then enters the scheduler loop to run applications in the hypervisor containers. The platform initialization routine is summarized in the Figure 26. The highlighted steps of the platform initialization routine are discussed further in the next section.

Figure 26. CODEZERO's platform initialization

### 3.3 CODEZERO port detail

#### 3.3.1 Zynq 7000 base address definitions

For CODEZERO to run on the ZedBoard, we need to modify some parts of the original source code for the Pandaboard. Firstly we need to change the register base addresses for all peripherals according to the Zynq 7000 hardware manual [22]. The essential base addresses for the Zynq 7000 platform [22] are defined in the file <code>include/l4/platform/zynq/offsets.h</code>, as shown in the Table 4.

Definition Description Physical address PLATFORM\_PHYS\_MEM\_START 0x0PLATFORM\_DEVICES1\_START 0xE0000000 Base address for I/O peripheral registers PLATFORM GICO BASE Base address for GIC 0 registers 0xF8F00100 PLATFORM\_SYSCTRL\_BASE 0xF8000000 Base address for system control registers PLATFORM\_UART1\_BASE Base address for console port 1 0xE0001000 PLATFORM\_TIMERO\_BASE 0xF8001000 Base address for triple timer 0 PLATFORM\_TIMER1\_BASE Base address for triple timer 1 0xF8002000 CPU1\_START\_ADDR\_BASE Start address for CPU1 core 0xFFFFFF0 FPGA\_CLOCK0\_BASE Base address for clock 0 for FPGA 0xF8000170 FPGA CLOCK1 BASE Base address for clock 1 for FPGA 0xF8000180 FPGA\_CLOCK2\_BASE Base address for clock 2 for FPGA 0xF8000190 FPGA\_CLOCK3\_BASE Base address for clock 3 for FPGA 0xF80001A0

Table 4. ZedBoard's base addresses

### 3.3.2 Rewriting the drivers

The UART, timer and generic interrupt controller (GIC) are all essential for CODEZERO's operation. The UART is used for console display and debug, the timer is used by the CODEZERO scheduler and the GIC is for hardware management. Other peripherals may be initialized and handle later by CODEZERO's guest OS (for example Linux or  $\mu$ C/OS). The drivers are in the *src/drivers* directory.

The modification to the GIC module is relatively trivial as there are no differences for platforms using the ARMv7 architecture. We simply need to change the base address of the GIC0 register to 0xF8F00100 in *offsets.h* (located in folder *include/l4/platform/zynq*).

For the UART, we have to change the base address (the address 0xE0001000) as well as initializing procedures due to changes in the register's organization in the Zynq 7000 platform. Because the UART is

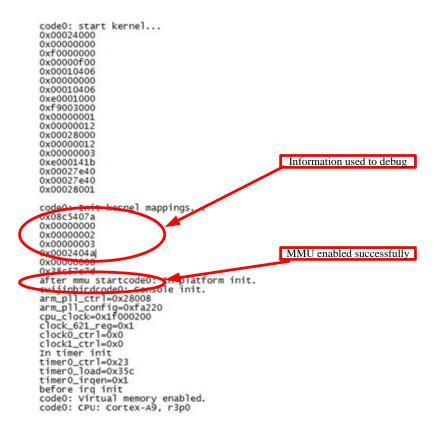

important for debug, it needs to be initialized earlier than the other peripherals. The updated driver file is *src/drivers/uart/pl101.c.* Before starting transmission and reception, we need to disable the transmit and receive paths, configure the character frame and baud rate, set the number of stop bits, and then enable the transmit and receive paths. In order to disable the transmit and receive paths, the ZYNQ\_RXE and ZYNQ\_TXE bits in the ZYNQ\_UARTCR (defined with the offset 0x0 in the file *include/l4/drivers/uart/pl101.h*) are cleared to 0, while ZYNQ\_RXDIS and ZYNQ\_TXDIS are set to 1. The UART character frame is configured by writing the value 0x00000020 to the register ZYNQ\_UARTMD (offset 0x4), enabling 8-bit character length, 1 stop bit, and no parity. Then, the CD value in the ZYNQ\_UARTBRG (offset 0x18) and the BIDV value in the ZYNQ\_UARTBRD (offset 0x34) are written to achieve the default baud-rate of 115200 bps for the default frequency of 50 MHz. Finally, the transmit and receive paths are enabled by setting ZYNQ\_RXE and ZYNQ\_TXE bits to 1 and clearing ZYNQ\_RXDIS and ZYNQ\_TXDIS to 0. After these changes, the UART in the ZedBoard starts to operate again as shown in Figure 27. Some common UART sequences are summarized in Table 5.

**Table 5. Common UART sequences**

| Name of sequence                   | Detail                                                           |  |  |

|------------------------------------|------------------------------------------------------------------|--|--|

| Transmit and receive paths disable | Clearing bits ZYNQ_RXE and ZYNQ_TXE in the                       |  |  |

|                                    | ZYNQ_UARTCR (equal to the PLATFORM_UART1_BASE                    |  |  |

|                                    | address with the offset 0x0)                                     |  |  |

| Character frame configuration      | Writing value 0x00000020 to ZYNQ_UARTMD (offset 0x4) to          |  |  |

|                                    | define a 8-bit length, 1 stop bit, and no parity character frame |  |  |

| Baud-rate configuration            | Writing appropriate values to CD field in ZYNQ_UARTBRG           |  |  |

|                                    | (offset 0x18) and BIDV field ZYNQ_UARTBRD (offset 0x34)          |  |  |

| Transmit and receive paths enable  | Setting bits ZYNQ_RXE and ZYNQ_TXE in the                        |  |  |

|                                    | ZYNQ_UARTCR to value 1                                           |  |  |

```

bootm 0

Booting kernel from Legacy Image at 00000000 ...

Image Name:

final.elf

2013-06-18

5:42:29 UTC

Created:

ARM Linux Kernel Image (uncompressed)

422420 Bytes = 412.5 KiB

Image Type:

Data Size:

Load Address: 02000000

Entry Point:

Verifying Ch

Loading Kerne

02000000

UART initialized

successfully

ng Kernel Image ... OK

Starting kernel ...

cuijinbird

copyright from NUT

ELF Loader: Loader image size: 412KB, placed at physical 0x2000000-0x2067214 machine nr: ff7f7fbd atags/dtb pointer: b7e0dcf7

Loading data placed from 0x20050a0 to 0x20672

Loading kernel...

Entry point: 0x358

Skipping program header section

Copying to range from 0x0 to 0x13858 of size: 0x13858

Clearing memory... starting from 13858, size: 0

Copying to range from 0x14000 to 0x19018 of size: 0x5018

Clearing memory... starting from 19018, size: 0

Copying to range from 0x1a000 to 0x1a000 of size: 0x0

Clearing memory... starting from 1a000, size: 60a0

Copying to range from 0x24000 to 0x38368 of size: 0x14368

Clearing memory... starting from 38368, size: 0

Loading cont0 .cont.0...

Loading .img.0 section image...

Entry point: 0xc0000000

Copying to range from 0x4004054 to 0x400405c of size: 0x8

Clearing memory... starting from 400405c, size: 0

Copying to range from 0x4000000 to 0x400405c of size: 0x405c

Clearing memory... starting from 400405c, size: 0

Copying to range from 0x4005000 to 0x40050b8 of size: 0xb8

Clearing memory... starting from 40050b8, size: 7090

```

Figure 27. The UART starts on ZedBoard

The timer is essential for the correct operation of the CODEZERO scheduler. In the ZedBoard, there is a 24-bit watchdog timer and two 16-bit triple timer/counters. We use triple timer/counter 0 (base address at 0xF8001000) as the clock source for the scheduler. It is initialized to use the *pclk* source with pre-scale mode enabled and the prescaler value set to 7 (i.e. the count rate is divided by (2^7+1)). Some common sequences for timer 0 are summarized in Table 6.

**Table 6. Common Timer sequences**

| Name of sequence              | Detail                                                             |  |  |

|-------------------------------|--------------------------------------------------------------------|--|--|

| Timer periodic initialization | Disable the timer by setting the DIS bit in the                    |  |  |

|                               | ZYNQ_TIMER0_CTRL (offset 0xC) register to high                     |  |  |

|                               | Select the clock input source, and set the prescaler value in the  |  |  |

|                               | ZYNQ_TIMER0_CLKCTRL (offset 0x0)                                   |  |  |

|                               | Choose the interval mode for the timer by setting the INT bit in   |  |  |

|                               | the ZYNQ_TIMER0_CTRL register                                      |  |  |

|                               | Enable the timer interrupt by setting corresponding bit of the IEN |  |  |

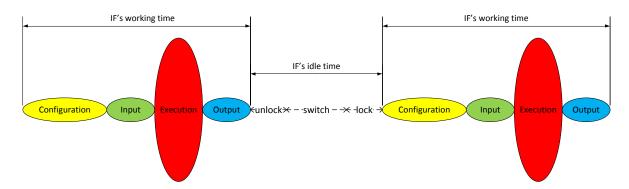

|                               | field in the ZYNQ_TIMER0_INTEN (offset 0x60) register              |  |  |