# A SCALABLE AND COMPACT LINEAR SOLVER WITH A FOCUS ON MODEL PREDICTIVE CONTROL

Ong Shen Hoong, Kevin

## School of Computer Engineering

A thesis submitted to the Nanyang Technological University in partial fulfillment of the requirements for the degree of Masters of Engineering

# **Statement of Originality**

| I hereby certify that the work embodied in this thesis is the result of |

|-------------------------------------------------------------------------|

| original research and has not been submitted for a higher degree to     |

| any other University or Institution.                                    |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

|                                                                         |

| Date Ong Shen Hoong, Kevin                                              |

## Acknowledgments

I would like to express my sincere gratitude and appreciation to my supervisors, Prof Suhaib A.Fahmy(SCE) and Prof Ling Keck-Voon(EEE) for the invaluable experience as your research student. To Prof Suhaib, for your patience, constructive and forward thinking comments especially when my research direction tilted towards a different outcome. To Prof Ling for teaching me how to crystallize my thoughts, proper technical writing and keeping me on my toes at all times. In addition, a special mention to Prof Ling for the rewarding experience gained from multiple roles during my secondment for the A\*STAR funded Embedded & Hybrid Systems II Programme (2008-2010).

Within NTU, I would like to thank various people at Centre for High Performance Embedded Systems (CHiPES) and EEE Control Engineering Lab. From CHiPES, Jeremiah Chua for his prompt IT system support and Vipin Kizheppatt for his helpful advice in digital hardware designs for FPGA. Not forgetting the MSc students(Nithin, Zain and Rakesh) who were willing to be my listening ear during the off-peak hours in CHiPES. From the Control lab, Thuy Dang Van and Zhou Dexiang for their help with control related jargons and latex programming respectively.

Last but not least, I would like to thank my wife Fangfang for her unwaivering love, patience, encouragement and company throughout the course of my study. Special mention to my parents and sister for their continuous encouragement and support on my decision for further studies.

## Abstract

Systolic Array architectures are data-flow based but designing architectures for solving specific problems can pose a challenge. In this thesis, an investigation into a scalable design for accelerating the problem of solving a dense linear system of equations using LU Decomposition is presented. A novel systolic array architecture that can be used as a building block in scientific applications is described and prototyped on a Xilinx Virtex 6 FPGA. The proposed linear solver has a throughput of approximately 1 million linear systems per second for matrices of size N=4 and approximately 82 thousand linear systems per second for matrices of size N=16. In comparison with similar work, the proposed design offers up to a 12x improvement in speed whilst requiring up to 50% fewer hardware resources. As a result, a linear system of size N=64 can now be implemented on a single FPGA, whereas previous work was limited to N=12 and resorted to complex multi-FPGA architectures to achieve the same effect. Moreover, the scalable design can be adapted to different sized problems with minimum effort.

# Contents

NANYANG TECHNOLOGICAL UNIVERSITY

| Acknowledgements                           | ;   |

|--------------------------------------------|-----|

| Abstract                                   | ii  |

| List of Contents                           | v   |

| List of Figures                            | ix  |

| List of Tables                             | xi  |

| List of Algorithms                         | xii |

| List of Abbreviations                      | xiv |

| 1 Introduction                             | 1   |

| 1.1 Linear Solver                          | 1   |

| 1.2 Scientific Computing Platforms         |     |

| 1.3 High-Level Design Approaches           | 4   |

| 1.3.1 Source-directed compilation approach |     |

| 1.3.2 Digital Signal Processing IP Cores   |     |

SINGAPORE

vi CONTENTS

|      | 1.3.3                                      | Model-based Approach                                                                                                                                                                               | 7                                                                                                                                                                                                                                                      |

|------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.4  | Resear                                     | ch Goals and Contributions                                                                                                                                                                         | 8                                                                                                                                                                                                                                                      |

|      | 1.4.1                                      | Publications                                                                                                                                                                                       | 9                                                                                                                                                                                                                                                      |

| 1.5  | Thesis                                     | Organization                                                                                                                                                                                       | Ĉ                                                                                                                                                                                                                                                      |

| Bac  | kgrour                                     | ıd                                                                                                                                                                                                 | 11                                                                                                                                                                                                                                                     |

| 2.1  | Model                                      | Predictive Control                                                                                                                                                                                 | 11                                                                                                                                                                                                                                                     |

| 2.2  | Systoli                                    | c Arrays                                                                                                                                                                                           | 16                                                                                                                                                                                                                                                     |

| 2.3  | Softwa                                     | re Linear System Solvers                                                                                                                                                                           | 20                                                                                                                                                                                                                                                     |

|      | 2.3.1                                      | Bluespec                                                                                                                                                                                           | 21                                                                                                                                                                                                                                                     |

|      | 2.3.2                                      | Xilinx System Generator                                                                                                                                                                            | 24                                                                                                                                                                                                                                                     |

| Lite | rature                                     | Review                                                                                                                                                                                             | 27                                                                                                                                                                                                                                                     |

| 3.1  | Linear                                     | Solver                                                                                                                                                                                             | 28                                                                                                                                                                                                                                                     |

|      |                                            |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                        |

|      | 3.1.1                                      | Algorithm Mapping using High-Level tools for FPGA                                                                                                                                                  | 28                                                                                                                                                                                                                                                     |

|      |                                            | Algorithm Mapping using High-Level tools for FPGA LU Decomposition on FPGA                                                                                                                         |                                                                                                                                                                                                                                                        |

|      | 3.1.2                                      |                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                     |

| 3.2  | 3.1.2<br>3.1.3                             | LU Decomposition on FPGA                                                                                                                                                                           | 28<br>31                                                                                                                                                                                                                                               |

| 3.2  | 3.1.2<br>3.1.3                             | LU Decomposition on FPGA                                                                                                                                                                           | 28<br>31<br>32                                                                                                                                                                                                                                         |

| 3.2  | 3.1.2<br>3.1.3<br>Linear                   | LU Decomposition on FPGA                                                                                                                                                                           | 28<br>31<br>32<br>33                                                                                                                                                                                                                                   |

| 3.2  | 3.1.2<br>3.1.3<br>Linear<br>3.2.1<br>3.2.2 | LU Decomposition on FPGA  Systolic Array implementations of LU Decomposition on FPGA  Solvers for MPC                                                                                              | 28<br>31<br>32<br>33<br>34                                                                                                                                                                                                                             |

| 3.3  | 3.1.2 3.1.3 Linear 3.2.1 3.2.2 Summ        | LU Decomposition on FPGA  Systolic Array implementations of LU Decomposition on FPGA  Solvers for MPC                                                                                              | 28<br>31<br>32<br>33                                                                                                                                                                                                                                   |

|      | 1.5  Back 2.1 2.2 2.3                      | <ul> <li>1.4 Resear</li> <li>1.4.1</li> <li>1.5 Thesis</li> <li>Backgroun</li> <li>2.1 Model</li> <li>2.2 Systoli</li> <li>2.3 Softwa</li> <li>2.3.1</li> <li>2.3.2</li> <li>Literature</li> </ul> | 1.4 Research Goals and Contributions  1.4.1 Publications  1.5 Thesis Organization  Background  2.1 Model Predictive Control  2.2 Systolic Arrays  2.3 Software Linear System Solvers  2.3.1 Bluespec  2.3.2 Xilinx System Generator  Literature Review |

CONTENTS

|   |                                                           | 4.1.1                                           | Bluespec Manual Declaration                           | 46                                     |

|---|-----------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------|----------------------------------------|

|   |                                                           | 4.1.2                                           | Bluespec Static Elaboration                           | 48                                     |

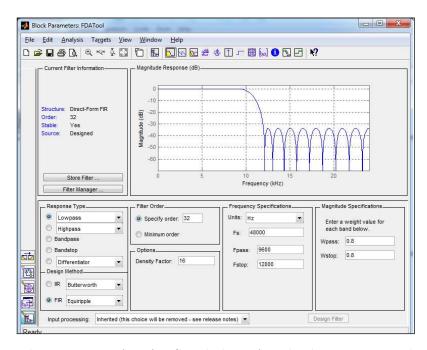

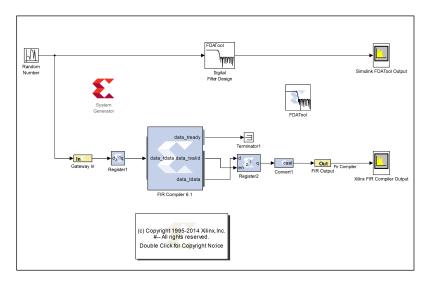

|   | 4.2                                                       | Direct                                          | -form FIR Filter - MATLAB Xilinx SysGen               | 50                                     |

|   |                                                           | 4.2.1                                           | MATLAB FIR Compiler                                   | 50                                     |

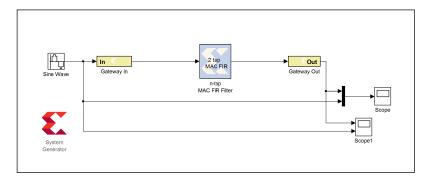

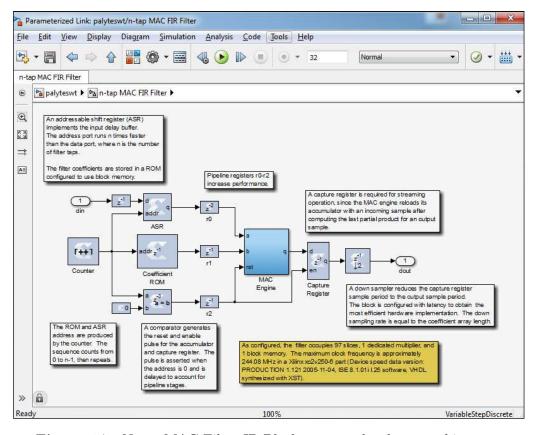

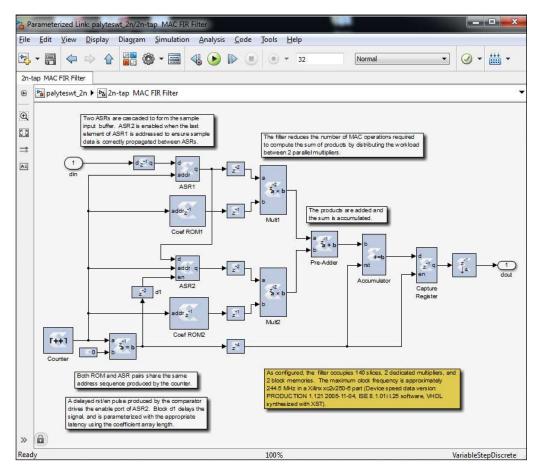

|   |                                                           | 4.2.2                                           | MATLAB MAC FIR Filter                                 | 52                                     |

|   | 4.3                                                       | Result                                          | ss                                                    | 54                                     |

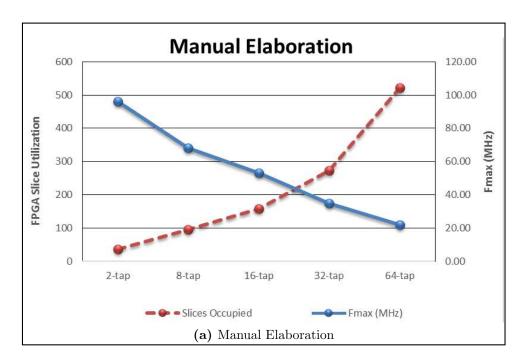

|   |                                                           | 4.3.1                                           | Bluespec                                              | 54                                     |

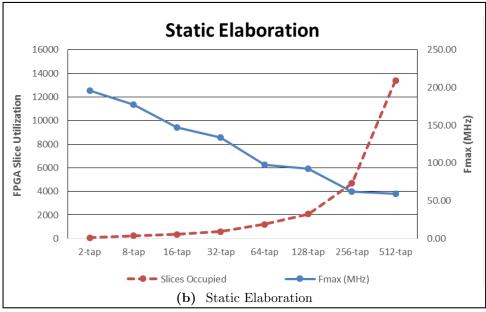

|   |                                                           | 4.3.2                                           | Xilinx FIR Filter Compiler                            | 55                                     |

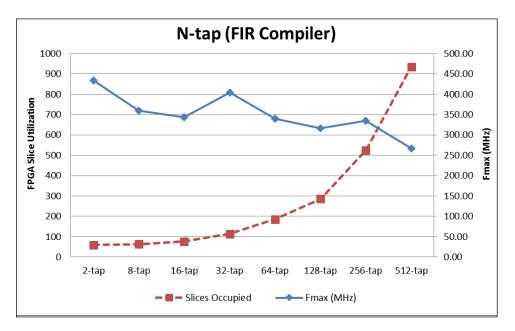

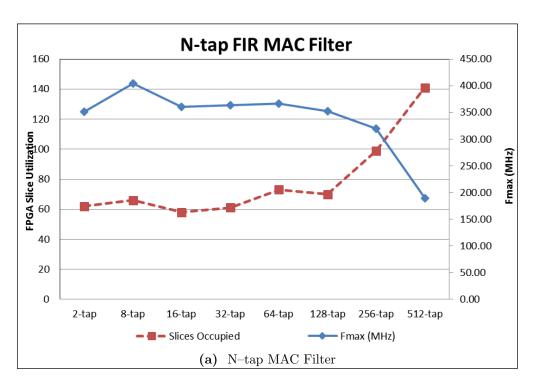

|   |                                                           | 4.3.3                                           | Xilinx MAC FIR Filter                                 | 55                                     |

|   | 4.4                                                       | Summ                                            | ary                                                   | 57                                     |

|   |                                                           |                                                 |                                                       |                                        |

| 5 | Pro                                                       | $\mathbf{posed}$                                | Hardware Solver Architecture                          | 61                                     |

| 5 | <b>Pro</b> 5.1                                            | -                                               | Hardware Solver Architecture Hardware Building Blocks |                                        |

| 5 |                                                           | TSA I                                           |                                                       | 61                                     |

| 5 | 5.1                                                       | TSA I                                           | Hardware Building Blocks                              | 61<br>63                               |

| 5 | 5.1<br>5.2                                                | TSA I                                           | Hardware Building Blocks                              | 61<br>63<br>66                         |

| 5 | 5.1<br>5.2                                                | TSA I Examp                                     | Hardware Building Blocks                              | 61<br>63<br>66<br>66                   |

| 5 | 5.1<br>5.2                                                | TSA I Example Proces 5.3.1                      | Hardware Building Blocks                              | 61<br>63<br>66<br>66<br>68             |

| 5 | 5.1<br>5.2                                                | TSA I Example Proces 5.3.1 5.3.2 5.3.3          | Hardware Building Blocks                              | 61<br>63<br>66<br>66<br>68             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | TSA I Example Procest 5.3.1 5.3.2 5.3.3 Triange | Hardware Building Blocks                              | 61<br>63<br>66<br>66<br>68<br>70<br>71 |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | TSA I Example Procest 5.3.1 5.3.2 5.3.3 Triange | Hardware Building Blocks                              | 61<br>63<br>66<br>66<br>68<br>70<br>71 |

viii CONTENTS

|    |       | 5.5.3   | Speedup                                 | 76 |

|----|-------|---------|-----------------------------------------|----|

|    |       | 5.5.4   | Proposed TSA Linear Solver Architecture | 76 |

| 6  | Imp   | olemen  | tation Setup and Results                | 81 |

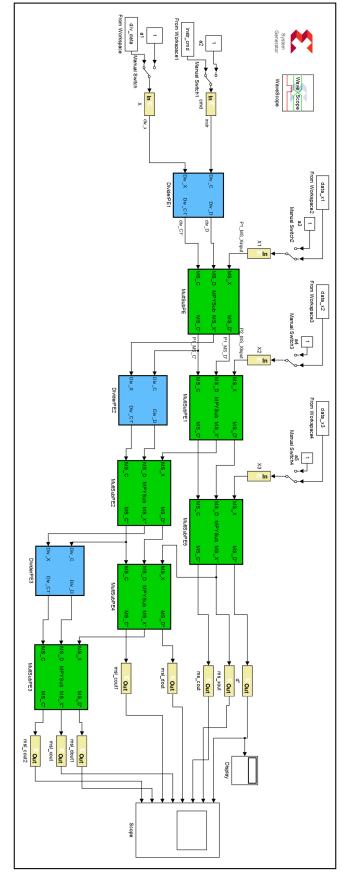

|    | 6.1   | System  | n Setup                                 | 81 |

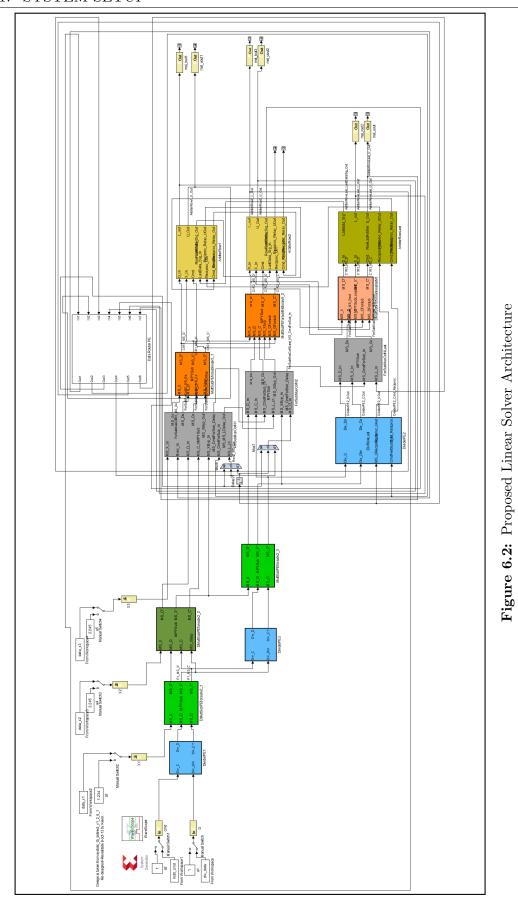

|    | 6.2   | Result  | s and Discussion                        | 85 |

|    |       | 6.2.1   | LU-TSA                                  | 85 |

|    |       | 6.2.2   | Linear Solver                           | 86 |

|    |       | 6.2.3   | Performance and Resource Scalability    | 88 |

|    |       | 6.2.4   | Summary                                 | 91 |

| 7  | Con   | ıclusio | n                                       | 93 |

| Bi | bliog | graphy  |                                         | 97 |

# List of Figures

| 1.1 | General-purpose Hardware Compilers [1]                                                                   | (  |

|-----|----------------------------------------------------------------------------------------------------------|----|

| 1.2 | Main Characteristics of various HLL C-to-FPGA Compilers [2]                                              | (  |

| 2.1 | Basic Structure of MPC [3]                                                                               | 12 |

| 2.2 | Similarities and differences of architectures (SIMD, MIMD, Systolic Arrays and Wavefront Arrays) [4] [5] | 17 |

| 2.3 | (a) Linear (b) Orthogonal (c) Hexagonal (d) Triangular [5]                                               | 18 |

| 2.4 | Classes of cells in systolic-type arrays                                                                 | 19 |

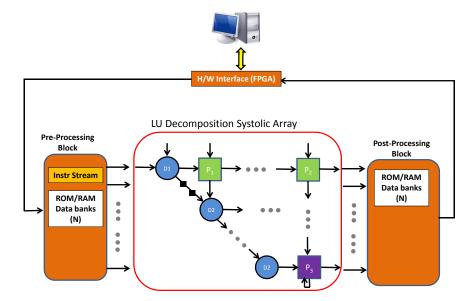

| 2.5 | Overall System Architecture                                                                              | 20 |

| 2.6 | Bluespec Design Flow [6]                                                                                 | 21 |

| 2.7 | Bluespec Software Module [6]                                                                             | 22 |

| 2.8 | Bluespec Simulation Speed Comparison [6]                                                                 | 24 |

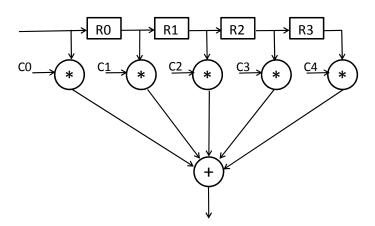

| 4.1 | Example of a 4-tap FIR Filter                                                                            | 45 |

| 4.2 | BSV Code for 8-tap FIR Filter using Manual Declaration                                                   | 47 |

| 4.3 | BSV Code for 8-tap FIR Filter using Static Elaboration                                                   | 49 |

| 4.4 | MATLAB Simulink FDATool Filter Design Tool                                                               | 51 |

| 4.5  | N-tap FIR Filter with Simulink FDATool Filter                                                          | 52 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 4.6  | Simulink code for N-tap FIR Filter using Xilinx FIR Compiler 6.1 IP  Block                             | 53 |

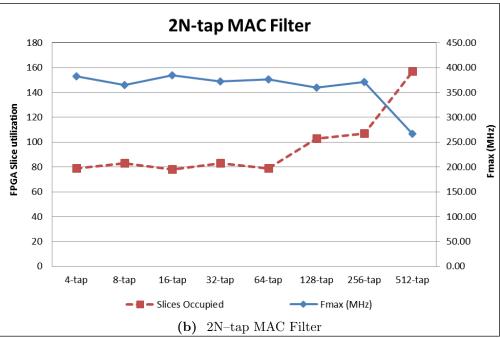

| 4.7  | N-tap MAC Filter IP Block compact hardware architecture                                                | 53 |

| 4.8  | 2N-tap MAC Filter IP Block compact hardware architecture                                               | 54 |

| 4.9  | Bluespec Resource and Performance Trade-off for N-taps FIR Filter  Design                              | 56 |

| 4.10 | Resource and Performance Trade—off for N—taps FIR Filter Design using Xilinx FIR Compiler 6.1 IP Block | 57 |

| 4.11 | Xilinx FIR Resource and Performance Trade–off for N–tap and 2N–tap MAC–based FIR Filter Design         | 58 |

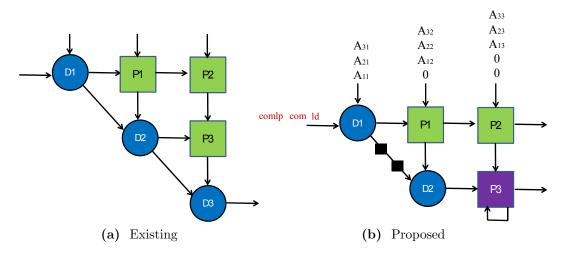

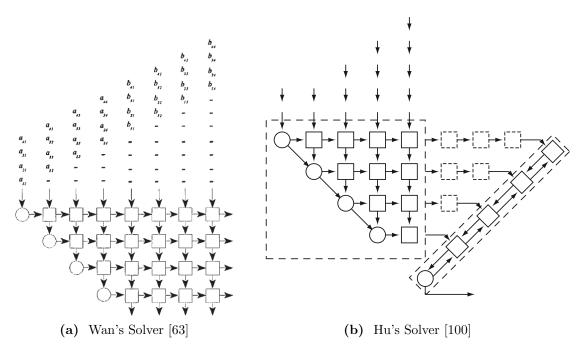

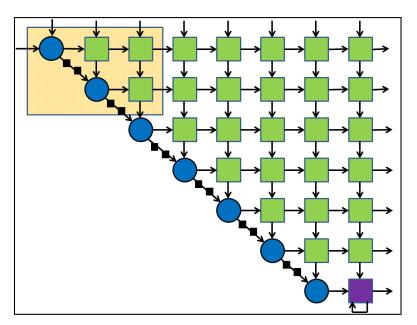

| 5.1  | Comparison of Triangular Systolic Array Architecture                                                   | 62 |

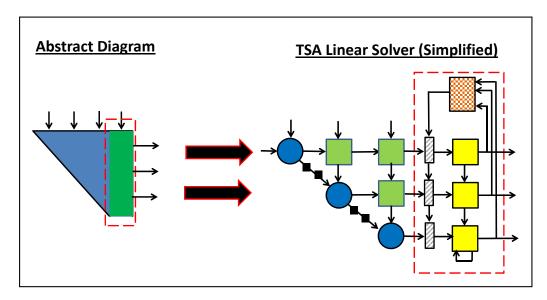

| 5.2  | Comparison of Basic TSA Design and Components                                                          | 63 |

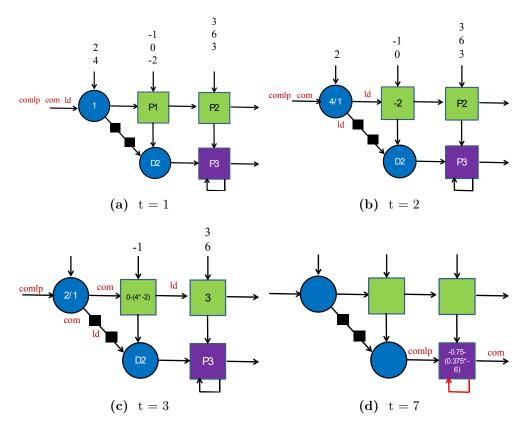

| 5.3  | Example TSA DataFlow for 3 x 3 LU Decomposition at different time-steps                                | 64 |

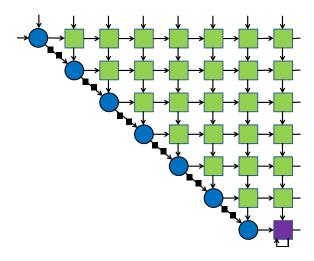

| 5.4  | 8 x 8 TSA Design for LU Decomposition                                                                  | 65 |

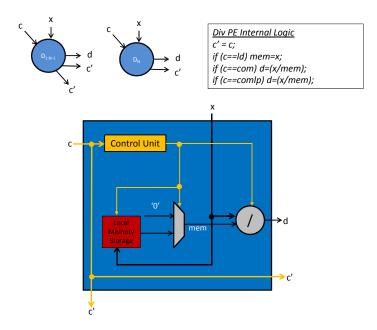

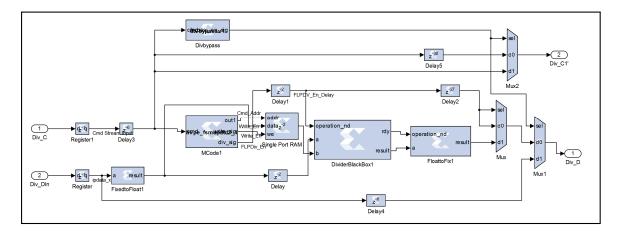

| 5.5  | Divider PE                                                                                             | 66 |

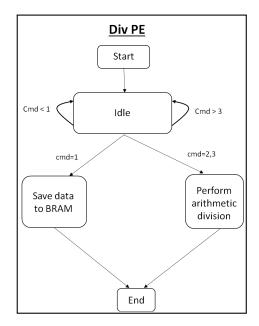

| 5.6  | State Diagram for Div PE                                                                               | 67 |

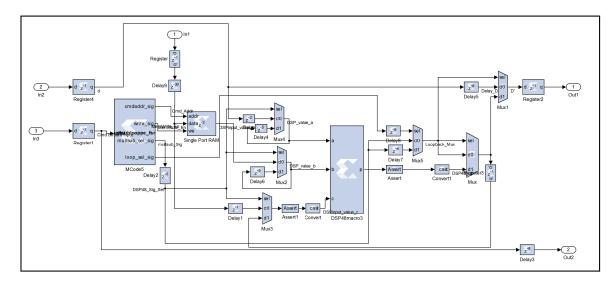

| 5.7  | Multiply-Subtract (MS) PE                                                                              | 68 |

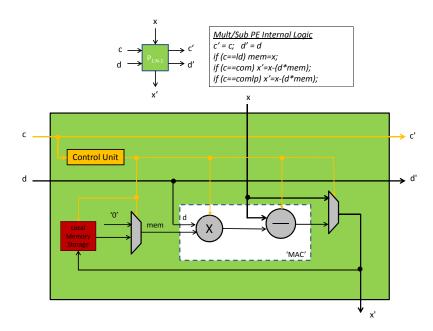

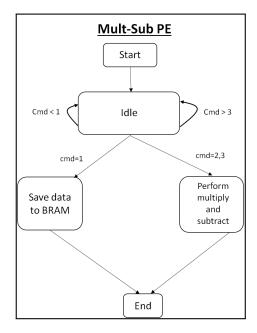

| 5.8  | State Diagram for Multiply-Subtract PE                                                                 | 69 |

| 5.9  | Modified Multiply-Subtract (MMS) PE                                                                    | 70 |

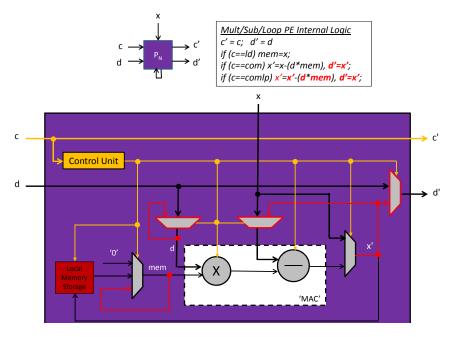

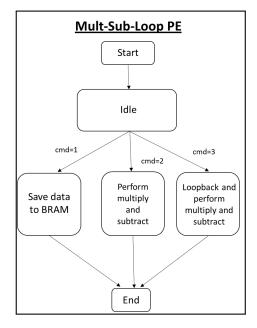

| 5.10 | State Diagram for Modified-Multiply-Subtract PE                                                        | 71 |

| 5.11 | Existing Linear Solver designs using Systolic Arrays                                                   | 72 |

| 5.1 | 2 Simplified System Architecture for proposed TSA Linear Solver                             | 77 |

|-----|---------------------------------------------------------------------------------------------|----|

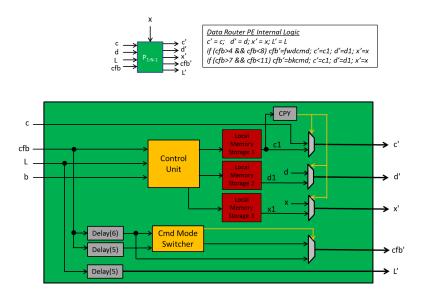

| 5.1 | 3 Data Router PE in proposed TSA Linear Solver                                              | 78 |

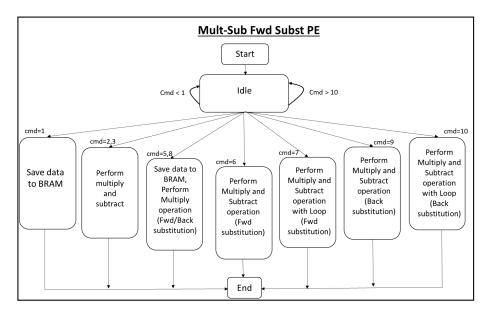

| 5.1 | 4 State Diagram for Multiply-Subtract Forward Substitution PE in proposed TSA Linear Solver | 79 |

| 6.1 | LU-TSA Hardware Architecture                                                                | 82 |

| 6.2 | 2 Proposed Linear Solver Architecture                                                       | 83 |

| 6.3 | 3 Internal logical blocks for Divider PE                                                    | 84 |

| 6.4 | Internal logical blocks for Multiply-Subtract PE                                            | 85 |

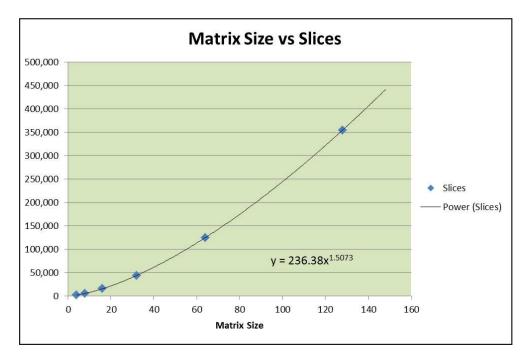

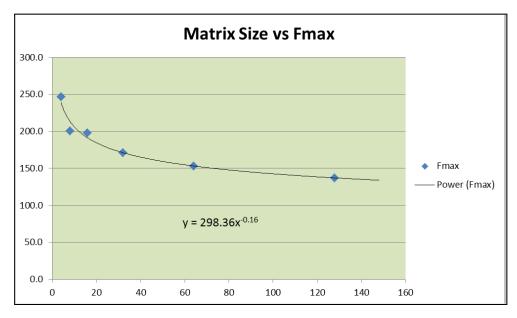

| 6.5 | Regression Model Results for Proposed TSA-based Linear Solver (Matrix Size vs Slices)       | 89 |

| 6.6 | Regression Model Results for Proposed TSA-based Linear Solver (Matrix Size vs Fmax)         | 89 |

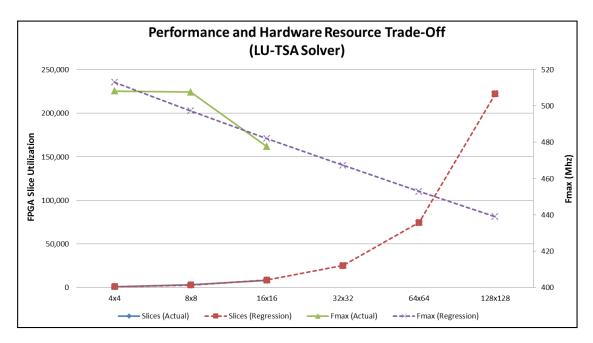

| 6.7 | 7 Hardware Performance and Resource Trade-Off for LU-TSA                                    | 90 |

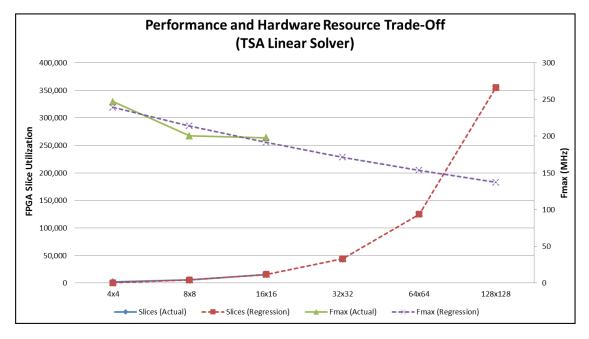

| 6.8 | Hardware Performance and Resource Trade-Off for Proposed TSA-based Linear Solver            | 90 |

| 6.9 | Design Scalability Example for TSA from $N=3$ to $N=8$                                      | 91 |

# List of Tables

| 3.1 | Summary of previous work                                          | 39 |

|-----|-------------------------------------------------------------------|----|

| 5.1 | Order of calculated values of L and U matrix output for $3x3$ TSA | 65 |

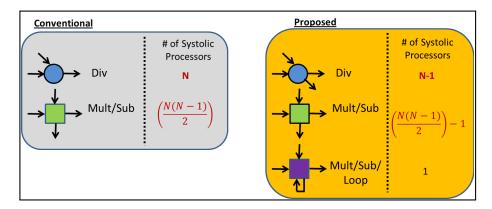

| 5.2 | Latency and PE Comparison with Similar Work                       | 75 |

| 6.1 | LU-TSA Performance & Resource Benchmarking                        | 86 |

| 6.2 | Linear Solver Performance & Hardware Resource Benchmarking        | 87 |

# List of Algorithms

| 1 Interior Point Method | _ L t. |

|-------------------------|--------|

|-------------------------|--------|

## List of Abbreviations

ASIC Application Specific Integrated Circuits

ASM Active Set Method

AST Altera Synthesis Tool

BLAS Algebra Subprograms

BRAM Block RAM

BSV Bluespec SystemVerilog

CGM Conjugate Gradient Method

CORDIC COordinate Rotation DIgital Computer

CUDA Compute Unified Device Architecture

DSP Digital Signal Processing

DSPB DSP Builder

EDK Embedded Development Kit

FGM Fast Gradient Method

FIR Finite Impulse Response

FPU Floating Point Unit

FRADL FPGA Regular Array Description Language

GPP General Purpose Processors

GPU Graphics Processor Unit

FPGA Field Programmable Gate Array

HDL Hardware Descriptive Language

HLS High-Level Synthesis

IPM Interior Point Method

KKT Karush-Kuhn-Tucker

LAPACK Linear Algebra PACKage

LNS Logarithmic Number System

LUD LU Decomposition

MAC Multiply-Add-Subtract

MIMO Multiple-Instruction-Multiple-Data

MIMO Multiple Inputs Multiple Outputs

MINRES Minimum Residual

MMS Modified Multiply-Subtract

MPC Model Predictive Control

NI National Instruments

NRE Non-recurring Engineering

OpenCL Open Computing Language

PE Processing Elements

QP Quadratic Programming

QRD QR Decomposition

RHS Righ-hand-side

RTL Register-Transfer-Level

SA Systolic Array

SDR Software Defined Radio

SIMD Single-Instruction-Multiple-Data

SVD Singular Value Decomposition

SysGen System Generator

TI Texas Instruments

TSA Triangular Systolic Array

TTM Time-to-Market

VCD Value Change Dump

VLIW Very Long Instruction Word

WLF Wave Log Format

XST Xilinx Synthesis Tool

# Chapter 1

## Introduction

#### 1.1 Linear Solver

A large portion of scientific computing is concerned with solving a system of linear equations through the use of numerical methods to give approximate but accurate solutions to computationally complex problems. Solving a system of linear equations is the basis of a number of scientific applications and two approaches are often used: iterative and direct methods. Iterative methods generate a sequence of approximations to the solution and the same computation procedure is performed in a repeated manner. Although iterative methods can be efficient both computationally and in terms of storage, a very good initial approximate value has to be chosen. This is because iterative methods are prone to numerical inaccuracies and convergence issues and the time taken to compute the exact solution becomes unpredictable. In contrast, direct methods determine the exact solution through a finite sequence of operations. As a result, the exact solution can be computed in a predictable amount of time and storage requirements can be estimated at design time.

## 1.2 Scientific Computing Platforms

As with all algorithmic implementations, development engineers usually survey a wide-range of mainstream computing platforms in the ever-changing landscape of computing architecture. The main reason for this change is due to the scaling limitations of clock frequency as chip manufacturers innovate to grapple with minimizing the amount of leakage current with each shrink in die size. More recently, semiconductor manufacturers have looked to increasing the amount of parallelism, and this has brought about the era of multi-cores with the latest General Purpose Processors (GPP), such as the Intel i7-3960X [7], featuring 6 cores, with each core operating at 3.3GHz and a combined onboard cache size of 15Mbytes. As general as a GPP is, real-world performance is usually much lower than the theoretical peak performance due to the fixed datapath and general architecture of the GPP computing platform. It is only recently that the software industry has caught up with chip manufacturers to exploit the computation power of multiple processor cores. In the past decade, two other scientific computing platforms have gained prominence for their alternative architectures, the Graphics Processor Unit (GPU) and the Field-Programmable Gate Array (FPGA), offering data parallelism to achieve significant hardware acceleration.

Modern day GPUs, such as those from AMD/ATI [8], contain hundreds of processor cores that can perform specialized matrix computation in a massively parallel manner, using the Very Long Instruction Word (VLIW) computing architecture. These devices boast high peak theoretical performance for single precision floating point [9], of the order of >1 TFLOP/s. But such performance is only achievable if sufficient parallelism can be applied, with some thousands of parallel threads, and provided there are no race conditions for read/write operations in the memory sub-system.

A different approach can be undertaken through the exploration of custom computing architecture. Application Specific Integrated Circuits (ASICs) are known

for having very high computation performance, low power consumption and offer a small die size. But the complexity of designing and validating such ASIC devices become a barrier as systems grow in design complexity and experienced hardware designers become scarcer. ASICs are known to offer long time-to-market (TTM), require high upfront costs and are only suitable for large volume applications. On the contrary, innovative advances in reconfigurable computing have made FPGAs a suitable platform for accelerating scientific computations. FPGAs boast fast TTM, low upfront costs and design errors can be rectified easily in the field unlike ASICs.

Recently, low to mid-range FPGAs have been embedded with dedicated hardware resources; Digital Signal Processing (DSP) blocks are included on-chip, equipping FPGAs with more computational muscle whilst providing deterministic execution time and low power consumption. With the availability of on-chip DSP blocks, most of the general FPGA fabric can be available for other hardware tasks. The highly optimized and onboard DSP blocks help accelerate the computational performance of DSP intensive algorithms. Given knowledge of the target FPGA architecture and embedded resources, hardware designers can better optimize their hardware design to exploit available embedded resources. A recent FPGA, Xilinx Zynq 7000 [10], includes an ARM dual-core Cortex A9 MPCore microprocessor, residing on the same silicon die as the general-purpose FPGA fabric. An implicit benefit of residing on the same silicon die is a high performance coupling of the two components.

On the design front, the availability of IP cores for common hardware peripherals seamlessly adds to the popularity of FPGAs. In addition, the productivity of hardware designers is increased and more effort can be spent in designing complex systems. A key disadvantage of FPGAs is design complexity compared to GPPs. The amount of onboard FPGA fabric required to synthesize the required hardware logic is also constrained by the efficiency of the design decisions made by the respective synthesis software tools.

FPGAs have previously been used to accelerate Model Predictive Control (MPC) and offer the benefit of hardware accelerated performance, but with the flexibil-

ity to tailor the implementation to the specific problem of interest. The majority of MPC researchers have focused on solving large problem sizes and their system solvers utilize iterative algorithms, such as the Conjugate Gradient Method, to handle sparse matrices. To achieve high linear solver performance, a digital hardware designer must customize the design at a low level of detail. But the design complexity in utilizing such linear solvers is well-beyond the reach of non-circuit designers and scientific researchers in general. Moreover, the ability to connect algorithms to hardware architectures and the use of high-level software tools for rapid design prototyping and parameterization is not exploited.

## 1.3 High-Level Design Approaches

The popularity of FPGAs, in realizing application-specific or hardware accelerator systems, is traditionally attained through the use of Hardware Descriptive Languages (HDL) such as VHDL and Verilog. In comparison with traditional high-level programming languages, the HDL-based design methodology provides a relatively low level of abstraction [11]. The pre-requisite for HDL design is prior/existing background knowledge and experience in digital design techniques, such as Register-Transfer-Level (RTL), in order to exploit the underlying FPGA architecture. Moreover, designing and troubleshooting of the application-specific design alone is time-consuming and this is why the use of FPGAs is limited to digital hardware design experts. The design complexity of state-of-the-art systems drives a strong need to have a technology independent modelling tool to model such complex systems while reducing the design effort required before the first prototype ASIC chip is taped-out to an IC package. Note that the cost of developing the ASIC chip amounts to millions of dollars and any design changes will further marginalize the companys profits per chip.

High-Level Synthesis (HLS) and compilers were created to promote the widespread use of FPGAs for both digital and non-digital hardware design specialists. The aim of HLSs is to allow the designers/programmers to rapidly create and model the complex systems before generation of RTL design code. For example, the HLS tools allow the designer to create a digital circuit, such as an embedded controller, with ease on an FPGA through the use of high level languages such as C, MAT-LAB and LabVIEW [12]. Hence, overall productivity of the designer/programmer is increased and more time can be spent on verifying the functional correctness of their customized system design. Examples of popular HLS tools include Handel-C [13], ImpulseC [14], Xilinx Embedded Development Kit (EDK) [15], MATLAB Simulink HDL Coder [16], National Instruments (NI) FPGA [12], Synphony [17], Vivado [18] and Bluespec [6]. The proposed approaches are discussed in the following sub-sections.

#### 1.3.1 Source-directed compilation approach

[1] surveyed the architecture and design methods aspect of reconfigurable computing for various applications. Various design approaches including general-purpose, special purpose, other design methods and emerging directions were reported. For general-purpose methods, [1] shortlisted the more significant hardware compilers and illustrated their corresponding use of various source and target languages, as shown in Figure 1.1.

Similarly in 2010, a comprehensive survey of C-to-FPGA tools was conducted by [2] and part of the survey focused on identifying the compilation method and the synthesis techniques applied, see Figure 1.2.

The findings in both [1, 2] suggest that C language is the preferred source language and the potential benefits of such an approach is well understood. To exploit the target FPGA hardware performance and resources efficiently, variants of C language are proposed to enhance the expressiveness of the C language for FPGAs. In addition, FPGA platform architectures vary for different manufacturers. As a result, more research efforts are required to make the source-directed compilation

| System               | Approach                         | Source language             | Target language                   | Target architecture           | Example applications                                    |

|----------------------|----------------------------------|-----------------------------|-----------------------------------|-------------------------------|---------------------------------------------------------|

| Streams-C [63]       | Annotation=<br>constraint-driven | C þ library                 | RTL VHDL                          | Xilinx FPGA                   | Image contrast<br>enhancement, pulsar<br>detection [78] |

| Sea Cucumber<br>[64] | Annotation=<br>constraint-driven | Java þ library              | EDIF                              | Xilinx FPGA                   | none given                                              |

| SPARK [65]           | Annotation=<br>constraint-driven | С                           | RTL VHDL                          | LSI, Altera FPGAs             | MPEG-1 predictor, image tiling                          |

| SPC [62]             | Annotation=<br>constraint-driven | С                           | EDIF                              | Xilinx FPGAs                  | String pattern matching, image skeletonisation          |

| ASC [71]             | Source-directed compilation      | Cþ þ using<br>class library | EDIF                              | Xilinx FPGAs                  | Wavelet compression, encryption                         |

| Handel-C [72]        | Source-directed compilation      | Extended C                  | Structural VHDL,<br>Verilog, EDIF | Actel, Altera<br>Xilinx FPGAs | Image processing, polygon rendering [79]                |

| Haydn-C [73]         | Source-directed compilation      | Extended C                  | Extended C<br>(Handel-C)          | Xilinx FPGAs                  | FIR filter, image erosion                               |

| Bach-C [77]          | Source-directed compilation      | Extended C                  | Behavioural and RTL VHDL          | LSI FPGAs                     | Viterbi decoders, image processing                      |

Figure 1.1: General-purpose Hardware Compilers [1]

|                   | Input Programming     | Granularity of    | 1 '                     |

|-------------------|-----------------------|-------------------|-------------------------|

| Compiler          | Language              | description       | Model Used              |

| Transmogrifier-C  | C-subset              | Operation         | Software, imperative    |

| PRISM-I. II       | C-subset              | Operation         | Software, imperative    |

| Handel-C          | Concurrency +         | Operation         | Delay, CSP model,       |

|                   | channels + memories   | - CP CHILDIN      | each assignment in      |

|                   | (C-based)             |                   | one cycle               |

| Galadriel & Nenya | Any language          | Operation         | Software, imperative    |

| 1                 | compiled to Java      |                   |                         |

|                   | bytecodes (subset)    |                   |                         |

| SPARCS            | VHDL tasks            | Operation         | VHDL and tasks          |

| DEFACTO           | C-subset              | Operation         | Software, imperative    |

| SPC               | C, Fortran: (subsets) | Operation         | Software, imperative    |

| DeepC             | C, Fortran: (subsets) | Operation         | Software, imperative    |

| Maruyama          | C-subset              | Operation         | Software, imperative    |

| MATCH             | MATLAB                | Operation and/or  | Software, imperative    |

|                   |                       | functional blocks |                         |

| CAMERON           | SA-C                  | Operation         | Software, functional    |

| NAPA-C            | C-subset extended     | Operation         | Software, imperative    |

|                   |                       |                   | added with              |

|                   |                       |                   | concurrency             |

| Stream-C          | C-subset extended     | Operation         | Software,               |

|                   |                       |                   | stream-based,           |

|                   |                       |                   | processes               |

| Garpcc            | С                     | Operation         | Software, imperative    |

| CHIMAERA-C        | С                     | Operation         | Software, imperative    |

| HP-Machine        | C++ (subset) extended | Operation         | Machines                |

|                   | to specify Machines   |                   | (process/thread)        |

|                   |                       |                   | Notion of update per    |

|                   |                       |                   | cycle                   |

| ROCCC             | C-subset              | Operation         | Software, imperative    |

| DIL               | DIL                   | Operation         | Delay notion, ?         |

| RaPiD-C           | RaPiD-C               | Operation         | Specific to RaPiD, par, |

|                   |                       |                   | wait, signal, and       |

|                   |                       |                   | pipeline statements     |

| CoDe-X            | C-subset, ALE-X       | Operation         | Software, imperative    |

| XPP-VC            | C-subset (extended)   | Operation         | Software, imperative    |

Figure 1.2: Main Characteristics of various HLL C-to-FPGA Compilers [2]

approaches sufficiently attractive for low-level circuit designers to adopt.

#### 1.3.2 Digital Signal Processing IP Cores

A typical drawback of using such high-level tools lies in the translation overheads, which result in non-optimum performance and inefficient use of the FPGAs on-chip resources, such as the inability to parallelize the hardware design sufficiently to gain higher system throughput, as seen in [19]. The availability of IP cores attempts to address such problems and is made available through software add-ons such as Xilinx Core Generator [20], Altera MegaCore Functions [21] and OpenCores [22], with an aim to reduce the development cycle to productively build modern day complex systems. To integrate and debug the IP cores with the existing logic, digital hardware designers require to be in the loop. The main disadvantage of using IP cores is the reliability of the IP core as bug fixes can only be issued by respective FPGA/CAD vendors and this introduces delay to the digital hardware designers already tight project schedule. As a result, architecture exploration becomes prohibitive when vendor-protected IP cores are involved. Similarly, OpenCores IPs are user-contributed and unoptimized with the option for user-modification to be made through HDL.

From the constraints mentioned, a model-based approach is more appropriate as the programming environment is graphical and data visualization becomes natural for non-circuit hardware designers.

## 1.3.3 Model-based Approach

The model-based approach utilizes graphical environments, such as MATLAB Simulink environment for design prototyping and verification of DSP applications on FPGAs. Once the functional hardware design have been verified, the downstream FPGA implementation steps involving synthesis and Place-and-Route are automat-

ically performed to generate an FPGA programming file. The two popular offerings are Xilinx System Generator (SysGen) [23] and Altera DSP Builder (DSPB) [24]. Compared with previous approaches, the model-based approach enables rapid creation of custom peripherals when compared to programmatic flow using HDL and previous experience with FPGAs is not required. In this thesis, the use of SysGen is selected for design prototyping and verification of a data-flow based hardware architecture for linear solvers.

#### 1.4 Research Goals and Contributions

In this thesis, we aim to propose a scalable and parameterizable linear solver as a building block in scientific applications, such as MPC. The structural regularity and scalability of the systolic array approach allows the linear solver to be rapidly prototyped using high-level software tools and non-circuit designers only need work at the architecture level. The proposed scalable systolic array architecture is not constrained to MPC and can be applied to general scientific computing problems where a system of linear equations is to be solved.

The major contributions of the thesis are as follows:

- 1. Exploitation of architectural parallelism, idle sequential cycles and omission of redundant arithmetic operations resulted in a novel systolic array hardware design architecture.

- 2. Scalable and wordlength parameterizable hardware architecture for easy adaptation to different sized problems with minimum effort.

- 3. Proposed linear solver performs floating-point division and has a throughput of about 1 million linear systems for matrices of size N=4 and about 82 thousand linear systems for matrices of size N=16.

- 4. Proposed design offers up to 12x improvement in solver speed whilst requiring up to 50% less hardware resources when compared to similar works.

5. A large linear solver of size N=64 can now be implemented on a single FPGA chip, whereas previous work was limited to N=12 and resorted to complex multi-FPGA architectures to achieve the same effect.

#### 1.4.1 Publications

A conference poster [25] has been accepted and presented in IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP) 2014.

## 1.5 Thesis Organization

This thesis is organized as follows. Chapter 2 presents a background on how solving a system of linear equations will accelerate scientific applications, such as Model Predictive Control (MPC) and presents the various design approaches to accelerate the linear solver. Chapter 3 summarizes prior work using general scientific platforms and FPGAs as a linear solver hardware accelerator. Chapter 4 presents a case-study to access the performance and hardware trade-off between Bluespec and MATLAB Xilinx SysGen tools using a direct-form FIR filter hardware design. Chapter 5 describes the proposed hardware architecture to enable design scalability. Chapter 6 presents the implementation setup and discusses the results in comparison with similar work. Chapter 7 describes the thesis' conclusion and highlights the outstanding issues for implementation as future work.

# Chapter 2

# Background

In this chapter, relevant background material is described. Firstly, the motivation for accelerating the system of linear equations in Model Predictive Control application is described. Secondly, an introduction to systolic arrays and existing work on LU Decomposition based linear solvers is presented. Thirdly, various high-level design approaches are reviewed. Finally, a brief overview of Bluespec and Xilinx System Generator tools are described for reader's reference prior to the case study experiment in Chapter 4.

#### 2.1 Model Predictive Control

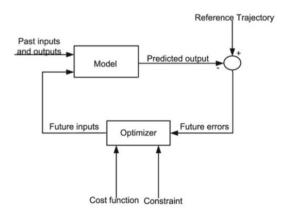

Model Predictive Control (MPC) is an advanced control method that is well established in the petrochemical industry. The natural ability in handling large multiple inputs multiple outputs (MIMO) systems with physical constraints makes MPC attractive. Characteristics of MPC include the moving horizon implementation, performance oriented time domain formulation, incorporation of constraints and explicit system model for use in predicting the future plant dynamics [3]. Typical components of MPC include the prediction model, objective function and obtaining the control law, as shown in Figure 2.1. Conventional MPC requires that the sam-

pling interval be greater than the time taken to solve the optimization problem [26] as it uses a model of the system to be controlled, to solve using numerical optimization methods. As the first part of the solution is implemented, the deviation error will occur between the next output measurement and the controller's predicted trajectory. Thus, the optimal control problem is only updated with new data after new measurement data has to be obtained at the next sample instant. This process is repeated for future sample instances.

Figure 2.1: Basic Structure of MPC [3]

The criteria for real-time MPC strongly depend on the speed at which the optimization problem is solved, in order to control the plant or system more quickly and effectively. In addition, the optimization problem requires sampling at high frequencies in order to capture fast occurring disturbances. That is why current applications of MPC are restricted to slow processes such as chemical plants, with sampling periods in the order of seconds although [27] reports growing research interest into the use of MPC in other areas such as ships, aerospace and micro scale devices. Therefore, it is useful to briefly understand the fundamental concepts on how Constrained MPC can be formulated as a Quadratic Programming (QP) problem.

Assume a discrete linear time-invariant plant with the following state space form:

$$\sum \begin{cases} x(k+1) &= Ax(k) + Bu(k) \\ y(k) &= Cx(k) \end{cases}$$

(2.1)

where  $y(k) \in \mathbb{R}^p, u(k) \in \mathbb{R}^m$  and  $x(k) \in \mathbb{R}^n$  represent the system output, input and internal states, respectively. The constrained MPC problem's objective is to minimize the cost function of:

$$\Phi(y, \triangle u) = \sum_{j=1}^{N_p} ||y(k+j) - \omega(k+j)||_q^2 + \sum_{j=0}^{N_{u-1}} ||\triangle u(k+j)||_r^2$$

where the cost function is subject to the following inequality constraints,

$$y_{LB} \le J_y y \le y_{UB} \tag{2.2}$$

$$x_{LB} \le J_x x \le x_{UB} \tag{2.3}$$

$$u_{LB} \le J_u u \le u_{UB} \tag{2.4}$$

$$\hat{u}_{LB} \le J_{\hat{u}} \triangle u \le \hat{u}_{UB} \tag{2.5}$$

The MPC problem can be converted into a QP problem [27] using the standardized approach by first replacing the predicted system output with the following definitions:

$$\Psi_{u} = \begin{bmatrix} CB & 0 & \cdots & 0 \\ CAB & CB & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ CA^{N_{P}-1}B & CA^{N_{P}-2}B & \cdots & CA^{N_{P}-N_{u}}B \end{bmatrix}$$

$$\Psi'_{u} = \begin{bmatrix} CA \\ CA^{2} \\ \vdots \\ CA^{N_{P}} \end{bmatrix} z = \begin{bmatrix} \Delta u(k) \\ \Delta u(k+1) \\ \vdots \\ \Delta u(k+N_{u}-1) \end{bmatrix}$$

Hence, the constrained MPC problem can be formulated as a compact QP problem:

$$\min_{z \in R^{n_v}} \left\{ \frac{1}{2} z' Q z + c' z : J z \le g \right\}$$

(2.6)

From equation (2.6),  $n_v = mN_u$  denotes the number of decision variables while  $Q = 2\Psi'_u\Psi_u + 2I$  is an  $n_v \times N_u$  positive definite Hessian matrix and  $c = 2\Psi'_u(\Psi_x x_k - \omega)$  is an  $n_v \times 1$  column vector. In addition, the size of J and g are  $m_c \times n_v$  matrix and  $m_c \times 1$  respectively, where  $m_c$  represents the total number of inequality constraints on z. Here,  $\omega$  is the set-point while  $N_p$  and  $N_u$  are the prediction and control horizons respectively.

At each sampling instance, the QP solver will generate the corresponding control signal to the plant. At the next sampling instance, the optimization solver process is repeated. The size and complexity of the optimization problem affects the computational requirements for online computation, condemning the use of MPC further. That is why the mentioned approach can be replaced with that proposed by Wright [28](pp. 91 of [29]), where the states and inputs during the prediction horizon are kept as variables, in order to get a banded Q matrix. The consequent solution of the linear system of equations, in both Interior Point Method (IPM) and Active Set Method (ASM), can be obtained more quickly for problems with large sizes. In the proposed research, we assume the MPC problems are insufficiently large to adopt the proposed QP formulation approach in [28].

Common methods for solving the QP problems are the ASM and IPM. In this thesis, IPM [30] is assumed and the Karush-Kuhn-Tucker (KKT) conditions for optimality is applied to the infeasible IPM for solving a QP problem. Thereafter, optimal control can be computed by applying Newton's method and the search direction can be obtained.

From Algorithm 1, it can be seen that step 3 is the most computationally intensive, which solves a system of linear equations,  $Ax=\hat{b}$ . Numerical methods such as Cholesky, Minimum Residual (MINRES), Conjugate Gradient Method (CGM),

#### Algorithm 1 Interior Point Method

```

1: Start IPM and select initial conditions

2: procedure Initialize (z^0, \lambda^0, t^0) with ((\lambda^0, t^0) > 0)

(z^k, \lambda^k, t^k)

3:

iteration,

solve

with:

where \Gamma = -(\Lambda^k)^{-1} T^k

Increment variables and check for convergence

4:

if Converge, then

5:

Stop and obtain optimal control z^{k+1}

6:

7:

8:

Return to step 3 and continue iteration

9:

end if

10: end procedure

```

Singular Value Decomposition (SVD), QR Decomposition (QRD), and LU Decomposition (LUD) are some of the approaches used for linear solvers.

In this thesis, we will focus on developing a linear solver for general use. Direct methods are preferred so as to enable efficient mapping to FPGAs and special matrix properties, such as symmetry and positive definite, are not considered. Secondly, the constraints and A matrix, in the compact QP problem, are assumed to be represented in a dense matrix data structure and the MPC problems are insufficiently large to adopt the proposed QP formulation approach [30] with high linear solver speed requirements,  $\geq 1000$  linear systems per second. One aspect of our proposed research is focused on utilizing an efficient and easy to implement numerical method for the linear solver. A single right-hand-side (RHS) is assumed and LU Decomposition is preferred as the method can be easily mapped to systolic arrays. To solve for a system of linear equations of size N, three steps are performed:

- 1. LU Decomposition A = LU

- 2. Forward Substitution  $L\hat{y} = \hat{b}$

- 3. Backward Substitution  $U\hat{x} = \hat{y}$

The computational complexity for LU Decomposition is  $\mathcal{O}(N^3)$  and requires division operations. The options for replacing the division operations are COordinate

Rotation DIgital Computer (CORDIC) [31], Givens Rotation and Conjugate Gradient Method to achieve division free operations. In this thesis, floating-point division is performed and the proposed use of Systolic Array architecture reduces computational complexity to  $\mathcal{O}(N)$ . In support of our systolic array approach, implementations of LU-based linear solver will be presented and discussed in Chapter 6.

#### 2.2 Systolic Arrays

Parallel execution of a problem can accelerate scientific computations with applications ranging from simulations to data mining. The common objective is to reduce time taken to solve large scientific problems by placing more emphasis on exploiting multi-processor hardware. If the single processing unit can accomplish the task in time T then N processing units could ideally accomplish it in time T/N, termed linear speed-up. But in most cases, the actual speed-up achieved on parallel computers is considerably smaller than the desired linear speed-up and this can be explained using Amdahl's law. Amdahl's law is often used to predict the theoretical maximum speedup for program processing using multiple processors. The maximum achievable speedup using N number of processors is  $\frac{1}{(1-P)+\binom{P}{N}}$ , where P is the proportion of a system or program that can be made parallel. Taxonomies to expose parallel architectures from different viewpoints have been reported by Flynn and Duncan [5].

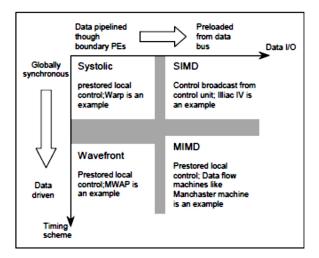

Systolic and wavefront arrays are also known as VLSI processor arrays and their differences are contrasted in Figure 1.1 along with Single-Instruction-Multiple-Data (SIMD) and Multiple-Instruction-Multiple-Data (MIMD) architectures. Systolic Arrays (SAs) are generally classified as high-performance, special-purpose VLSI computer systems that are suitable for specific application requirements that must balance intensive computations with demanding I/O bandwidths. SAs are organized as networks comprising a large number of identical, locally connected elementary Processing Elements (PE). A global clock synchronizes data between the PEs. Data in SA are rhythmically pulsed from memory through PEs before returning to mem-

**Figure 2.2:** Similarities and differences of architectures (SIMD, MIMD, Systolic Arrays and Wavefront Arrays) [4] [5]

ory. Hence, only the initial data and final results are transferred between the host and the systolic array.

A computing network may be considered a SA provided it exhibits the following characteristics: Network, Rhythm, Synchrony, Modularity, Regularity, Locality (Spatial/Temporal), Boundary, Extensibility and Pipelinebility; Network and rhythm have been mentioned previously. Synchrony refers to the behaviour of data that is rhythmically computed, by global clock, and passed through the network for execution of instructions and communication purposes. Modularity refers to the finite/infinite array consisting of modular processing units. Regularity refers to a homogeneously interconnected modular processing unit. Spatial locality refers to the local communication between cells. Temporal locality refers to the signal transmission characteristic of at least one unit time delay between cells. Boundary processors are the PEs are the only ones allowed to communicate with the outside world. Pipelinebility is a synonym for data pipelining where at least one delay element is found or inserted between two directly connected combinatorial PEs for the purpose of achieving high speed.

The concept of SAs to achieve data parallelism was introduced by [32] and global communication was an issue for large hardware designs. [32] noted that mathe-

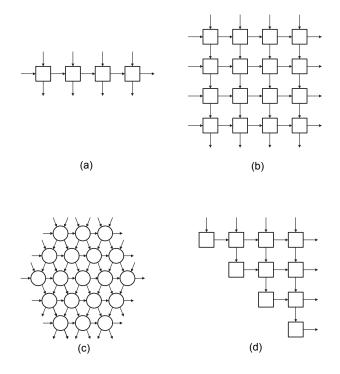

Figure 2.3: (a) Linear (b) Orthogonal (c) Hexagonal (d) Triangular [5]

matical pivoting was more for storage minimization rather than global communication and subsequently proposed two triangularization concepts, triangularization with neighbour pivoting and orthogonal triangularization, with an aim of minimizing global communication. Some examples of SA structures are linear arrays, orthogonal, hexagonal and triangular structures which can be implemented in a variety of hardware technologies, see Figure 2.3. Despite being proposed three decades ago, SAs are still an important research area for high performance computing applications [33]. Some applications of SAs include Multiple Input Multiple Output (MIMO) Software Defined Radio (SDR) [34], Block Matching Motion Estimation [35], and QR Decomposition for radar mapping applications [36]. The homogeneous multiprocessor array permits matrix computations naturally and enables high-level computations to be easily mapped into hardware structures through regular and reconfigurable pipelined processor cells.

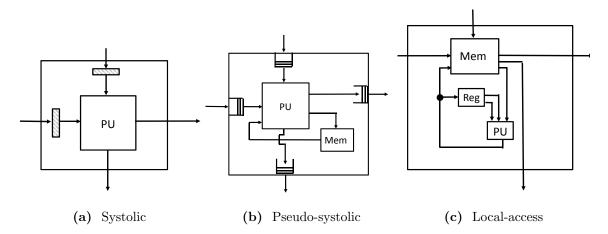

In relation to communication bandwidth and internal storage, three classes of systolic-type arrays exists, namely systolic cell, pseudo-systolic cell and local-access

Figure 2.4: Classes of cells in systolic-type arrays

cell. In this thesis, the author assumes off-chip memory degrades the overall system performance and on-board memory is to be exploited on the resource-constrained FPGA platform. Hence, the *pseudo-systolic cell* type of SA is selected, see Figure 2.4. Readers are referred to [37] for more details of each class of systolic-type array.

Although SAs are organized as networks comprising of a large number of identical, locally connected elementary Processing Elements (PE), a global clock is required to synchronize data between the PEs. Data in the SA is rhythmically pulsed from memory through PEs before returning to memory. Such synchronous behaviour may not be needed on all applications and can cost resources. Hence, the use of modern high-level software tools is proposed to reduce the time-to-market and non-recurring engineering costs for implementation on low-cost FPGA platforms.

The simple design of the PE suggests that SA design is easily scalable and can achieve high data throughput. In cases where design size is limited by available hardware resources, SAs may also be configured to operate as a high performance coprocessor to accelerate numerical calculations and communication with an external controller is performed through a high speed interconnect bus, see Figure 2.5. A case in point is where triangular systolic array for the matrix triangularization step is proposed to reduce computational complexity to  $\mathcal{O}(N)$ . The reader is assumed to

Figure 2.5: Overall System Architecture

be familiar with matrix decomposition methods and LU decomposition is preferred as the method is easily mapped to systolic arrays.

### 2.3 Software Linear System Solvers

Software libraries, such as Basic Linear Algebra Subprograms (BLAS) and Linear Algebra PACKage (LAPACK), exist to solve systems of linear equations on GPPs and GPUs. While there are many published research works on BLAS and LAPACK for FPGAs [38], the libraries are highly customized and require circuit hardware designers to be in the loop. To realize our research objective of a scalable linear solver for non-circuit designers, the use of high level synthesis tools, such as Bluespec and Xilinx System Generator, are highly desirable and are briefly examined in this chapter. To determine the suitable high-level software environment, a case study was performed to compare and contrast both synthesis tools and performance results are discussed in details in Chapter 4.

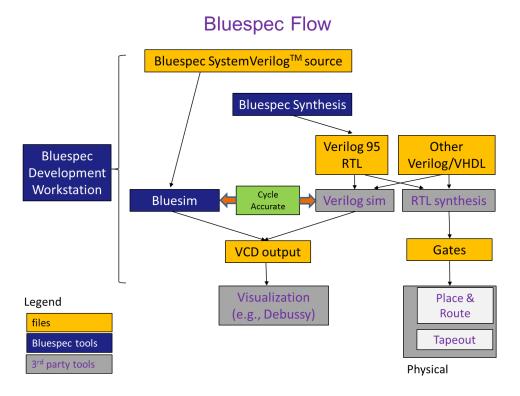

#### 2.3.1 Bluespec

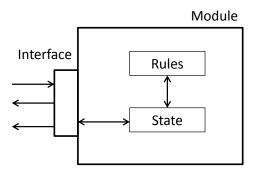

Bluespec [39] is a state-of-the-art platform tool that is utilized for the purpose of hardware system design specification, synthesis, modeling and verification [40]. To date, Bluespec has been used in the area of modeling for software development, modeling for architecture exploration, verification and IP creation. As with other HDLs, Bluespec designs are modular and each Bluespec module communicates through an interface, instead of ports. A module is used to represent hardware circuits in Bluespec, similar to Verilog module. Each module consists of 3 basic aspects namely states, rules and interfaces, as shown in Figure 2.6.

Figure 2.6: Bluespec Design Flow [6]

The states are represented as hardware registers, flip-flops and memories. Rules are used to execute operation logic to satisfy/modify the state values and each module can contain multiple rules. Each interface consists of methods, akin to methods in object-oriented programming (OOP) languages, and inherits the advantage of OOP for large system designs. For communication between interfaces, Bluespec has implicit guards on the methods, which specify when a method is ready for firing.

The language, Bluespec SystemVerilog (BSV), is based on Haskell and the rule-based approach, known as Guarded Atomic Action, is used to describe hardware behaviour. BSV programs can be understood in terms of atomic rule firings in the hardware design and traditional hardware model of finite state machine is used to implicitly express concurrent operations. In instances where multiple rules are concurrently executed, the Bluespec compiler is able to generate a combinational

Figure 2.7: Bluespec Software Module [6]

scheduler, which efficiently schedules the rules in each cycle. In the event where the Bluespec compiler is unable to decide, feedback will be provided to notify and guide the hardware designer in making better design decisions. For example, if the Bluespec compiler determines that two rules cannot be concurrently fired and additional combinational logic is required, the designer will have to explicitly specify his preference to the compiler. Thereafter, the compiler is able to work through all rules and apply Boolean optimizations to simplify the hardware design further resulting in the generation of a complete schedule. The rule-based design is compiled and translated into RTL implementation, as shown in Figure 2.7. Likewise BSV has in-built support for importing Verilog IP and C code into BSV designs through the use of wrappers.

Bluespec is strongly type-checked to reduce the amount of logic bugs, a feature commonly found in traditional Hardware Descriptive Language (HDL). For easier understanding of synthesizable hardware, state elements have to be explicitly created. According to [41], the BSV-coded Verilog can approach the quality of hand-coded Verilog design as supported by the work described in [42] where a comparative evaluation of a Reed-Solomon Decoder was performed between a C-based design flow and Bluespec. [42] pointed out that the advantage of a C-based synthesis tools compiler decreases as data-dependant control behaviour in the program increases, leading to inefficient hardware. Even in the hands of an experienced hardware designer, considerable effort is still required for architecture design exploration. On the other hand, [42] acknowledged that while Bluespec simplifies the algorithm into relatively simple modular structures, micro-architecture exploration is still required on a per application basis. Bluespec architectural exploration can be expected in the proposed research work.

Additional facilities of Bluespec include Bluesim, a native simulator and sourcelevel debugger, touted to provide 5-50x speed improvements over Verilog simulation through exploitation of the computation model. A table of comparison between Bluesim and a commercial RTL simulator is presented in Figure 2.8. Bluesim has in-built debugging options to enable/disable viewing of scheduling activities and generates 2 signals, "CAN\_FIRE\_rulename" and "WILL\_FIRE\_rulename". The "CAN\_FIRE\_rulename" occurs when the rule predicate (both implicit and explicit) conditions are all met. The "WILL\_FIRE\_rulename" occurs only when the scheduler allows the rule to fire [54]. Other powerful features include simulating until clock, single step, examining of signals and so on. Type-checking and schedule analysis are also available from Bluesim. Bluespec does not constrain user debugging and simulation to Bluesim. In fact, Bluespec is also able to support 3rd-party EDA simulators and waveform viewers such as nWave, gtkWave and ModelSim [43] through generation of a Value Change Dump (vcd) file. When the case-study was performed, Bluespec does not support any feature to enable automatic conversion of vcd files to Wave Log Format (wlf) for import into 3rd-party EDA simulators and waveform viewers. To automate this process, the author created a batch file and integrated the batch file for execution as a post-compiler command so as to allow non-circuit

| Designs               | Bluesim<br>(secs) | Fastest RTL<br>Simulator<br>(secs) | Speedup<br>(factor) |  |  |  |  |

|-----------------------|-------------------|------------------------------------|---------------------|--|--|--|--|

| Wide GCD              | 5.53              | 39.7                               | 7.18x               |  |  |  |  |

| Life Game             | 8.37              | 283                                | 33.9x               |  |  |  |  |

| FIR Filter            | 4.23              | 61.8                               | 14.6x               |  |  |  |  |

| Upsize<br>Converter   | 53.98             | 98.7                               | 1.83x               |  |  |  |  |

| Wallace<br>Multiplier | 48.66             | 417.0                              | 8.57x               |  |  |  |  |

| FIFO                  | 11.73             | 124.2                              | 10.6x               |  |  |  |  |

| Mesa                  | 37.45             | 126.4                              | 3.37x               |  |  |  |  |

| DIV3                  | 8.24              | 116.8                              | 14.2x               |  |  |  |  |

| DES Core              | 28.55             | 89.36                              | 3.13x               |  |  |  |  |

| IDCT                  | 15.69             | 16.32                              | 1.04x               |  |  |  |  |

Figure 2.8: Bluespec Simulation Speed Comparison [6]

designers to verify and display the generated BSV design waveform in ModelSim. Although the absence of the file conversion feature is minor, it could affect the mass adoption of Bluespec for non-circuit designers.

In summary, BSV inherits its powerful abstraction features from advanced programming languages and offers rich user-defined polymorphic types and overloading, strong static type-checking, first class parameterization and higher-order programming, recursion and object-oriented (transactional) interfaces.

#### 2.3.2 Xilinx System Generator

Xilinx System Generator (SysGen) for DSP is a system-level modeling tool which offers libraries, containing logic blocksets which are bit-true and cycle-accurate models, and is offered as a plug-in into MATLAB Simulink tool. With over 90 DSP building blocks are provided in the Xilinx DSP blockset for Simulink, these blocks leverage the Xilinx IP core generators to deliver optimized results for the target FPGA device. All of the downstream FPGA implementation steps, including synthesis and place and route, are automatically performed and an FPGA programming file is generated in the end for downloading into the FPGA platform.

Other features of SysGen includes System Resource Estimation to take full advantage of the FPGA resources, Hardware Co-Simulation and accelerated simulation

through hardware—in—the—loop co-simulation, providing many orders of simulation performance increase. SysGen can also function as a system integration platform for the design of DSP FPGAs that allows the RTL, Simulink, MATLAB and C/C++ components of a DSP system to come together in a single simulation and implementation environment. As a result, error-free designs can be quickly prototyped in MATLAB environment and researchers only need focus on functional verification of their hardware architecture design.

In this thesis, the proposed SA hardware architecture is data-flow based and SysGen is the suitable graphical programming environment to help us achieve our research goals.

# Chapter 3

## Literature Review

In recent years, the increased proliferation of low-cost multi-processor systems has garnered growing interest from researchers wishing to utilize high performance computing platforms for high bandwidth control applications, such as ships, aerospace, robotics and automotive [44]. One popular approach is to offload high computational burdens onto reconfigurable hardware accelerator platforms such as Field Programmable Gate Arrays (FPGAs). When compared with custom application-specific integrated circuit (ASIC) designs, FPGAs are a preferred platform choice as they offer high design flexibility, shorter Time-To-Market (TTM) design cycles with low upfront non-recurring expenses (NRE). When compared with other popular high performance computing platforms, [45] has dispelled the common doubt of FPGA not being up to the task for handling real-time MPC.

In this chapter, the objective is to review the various approaches to realizing fast linear solvers for general scientific applications on FPGAs. At the same time, we will also review and present the various approaches to realizing fast linear solvers for MPC applications across various computing platforms. Finally, the findings are summarized and the proposed research contribution is briefly mentioned.

#### 3.1 Linear Solver

#### 3.1.1 Algorithm Mapping using High-Level tools for FPGA

The concept of matrix decomposition, using FPGA technology, for the purpose of hardware acceleration or application-specific applications is still an active research area with researchers [46–50] proposing the use of high-level methods to map the LU Decomposition algorithm onto FPGA architecture. Meanwhile the majority of researchers looked into application-specific architectures to accelerate the LU Decomposition techniques on FPGA. For example, [46] proposed the FPGA Regular Array Description language (FRADL) for automatic mapping while [47] demonstrated the use of Fortran to construct non-pivoted LU Decomposition. [48,49] proposed design methodologies, such as bijective space-time transformation, to enable mapping of LU decomposition into linear systolic arrays with no reported implementations. [50, 51] proposed the use of their tool for automatic architecture generation and optimization. They used their proposed tool to implement a variety of matrix inversion solvers using Cholesky, QR, LU. They implemented their design on a Xilinx Virtex-4 XC4VSX35 FPGA for a 4 x 4 matrix using a 20-bits fixed-point precision and achieved a design operating frequency of 166MHz with a linear solver performance of approximately 0.35 million linear systems per second. In addition, [34] implemented their QR Decomposition-based Recursive Least Squares (QRD-RLS) design on a Xilinx Virtex-4 XC4VLX200 FPGA using floating point precision and reported a design operating frequency of 115MHz with a linear solver performance of 0.15 million linear systems per second.

#### 3.1.2 LU Decomposition on FPGA

Mathematical pivoting is used in numerical algorithms, such as Gaussian elimination and LU Decomposition, to ensure numerical stability to the final result obtained. To do so, tracking of the sorted rows and columns in a matrix is required and moving of elements, within the matrix, adds performance overhead to the algorithm. As a result, the author noted that majority of the research efforts were focused on LU decomposition without pivoting until 2009. In this section, a brief literature review of LU Decomposition implementation variants, with and without pivoting, will be presented.